# Electronics FE/DAQ/DCS Leonid Afanasyev

### Compilation of presentations at SPD Hardware meetings on 25 March and 29 April 2021

### Estimation of raw data flow

Bunch crossing each 80 ns; crossing rate 12.5 MHz, Collision rate ~3–4 MHz → Triggerless DAQ to avoid any hardware biases

Data flux was estimated for the maximum luminosity  $L = 10^{32} \text{ cm}^{-2}\text{c}^{-1}$ and maximum energy  $\sqrt{s} = 27 \text{ GeV}$ .

Within simplified simulation and some safety margin the data flux is estimated as 20 GBytes/s.

## Front-end electronics for the free-running DAQ-SPD

Front-end electronics of the detectors has to meet the requirements of a free-running DAQ

<u>General FEE requirements</u> from the DAQ system:

- Self-triggered (*trigger-less*) FEE operation

- Digitizing on-board

- Zero suppression

- Large memory to store the data accumulated in a time slice

- $\odot$  Timestamp included in the output format

- Compatibility with DAQ (AMBER/NA64)

- Optic output

- Protocols: S-link, Aurora, UCF

- White Rabbit input (option)

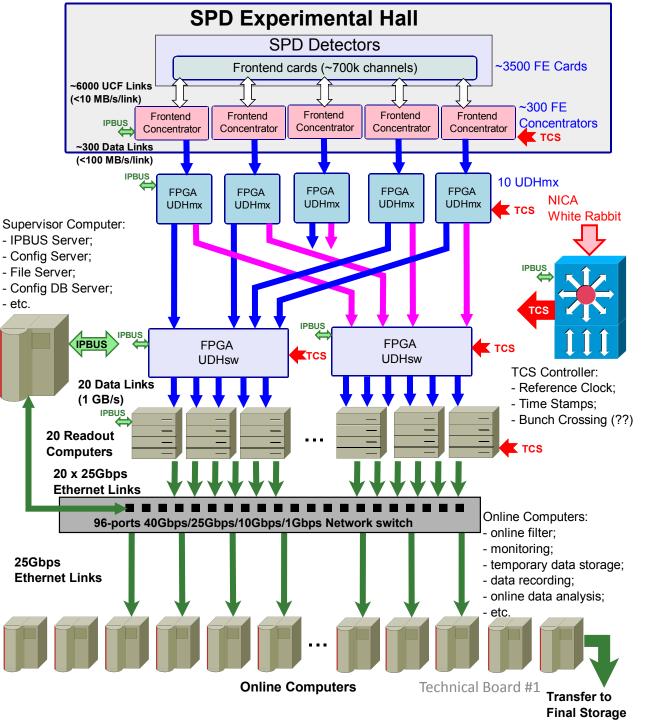

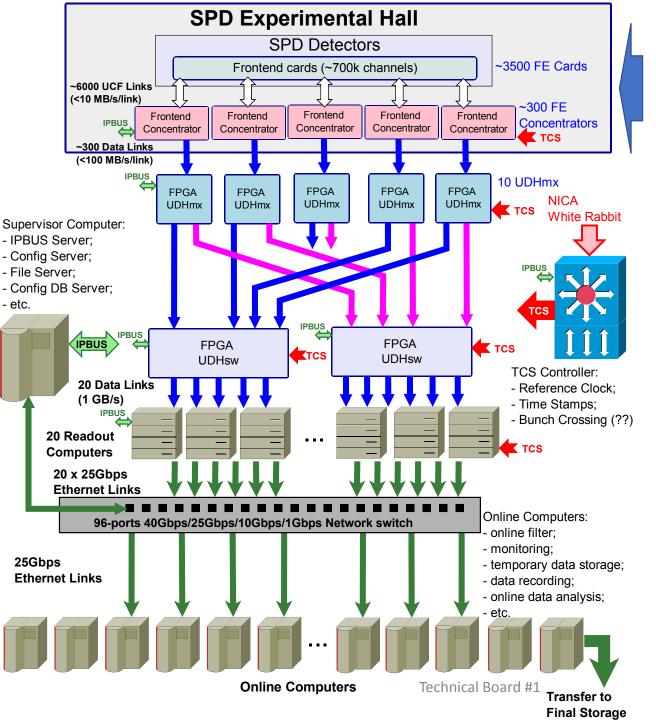

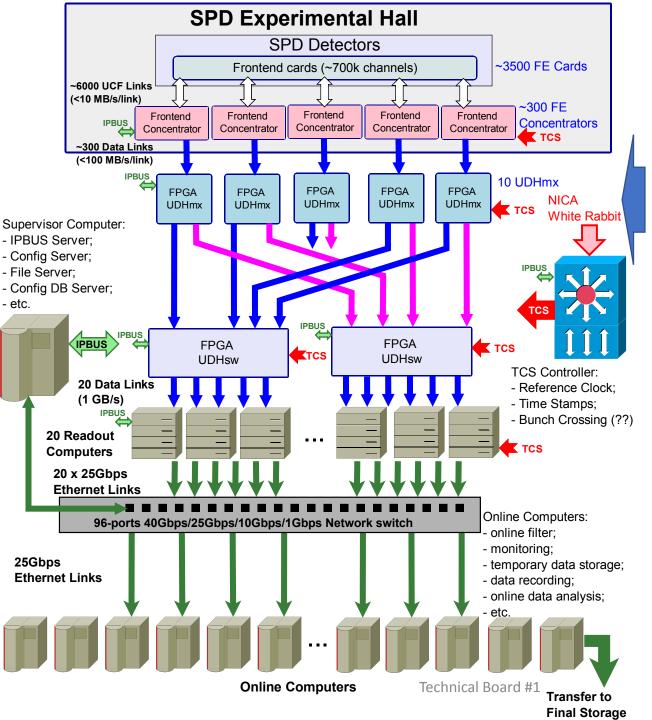

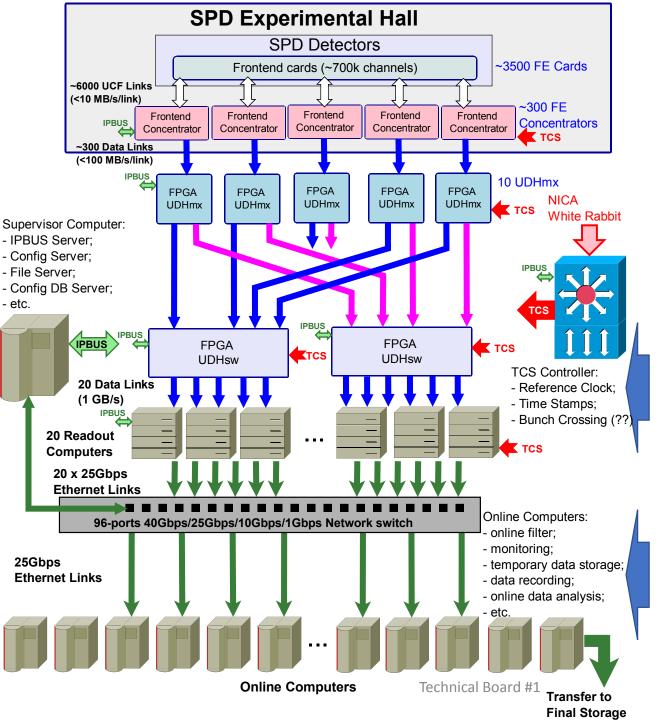

In DAQ of SPD we are planning to employ the ideas developed for the modernized DAQ of COMPASS/AMBER/NA64 by Igor Konorov group from the Technische Universität of München (TUM). His conception of SPD DAQ is accepted with minor modifications.

Slow control accesses FE cards via the FE Conccentrators using UDP-based IPBus protocol.

FE Conccentrators retransmit clock signals to FEE and convert detector information to a high speed serial interface running over an optical link. UCF (*Unified Communication Framework*) protocol will be a standard high speed link

protocol within the DAQ.

#### The multiplexer (UDHmx)

modules receive detector information via serial links, verify consistency of data, and store them in DDR memories.

The multiplexer is equipped with 32 GBytes of memory.

All accepted data are assembled in sub-slice and distributed to two switches. Each multiplexer has a bandwidth of 2 GBytes/s.

#### The switches (UDHsw)

perform the final level of slice building and distribute the assembled slices to 20 (?) online computers.

Finally, the continuous sequence of slices is built with Network Switch in each PCs

# DAQ hardware

#### **Near detector**

Mechanics:

- 374 Front End Concentrators VME 6U double width 12(15) inputs, 1 outputs

- 43 VME crates,  $0.5kW \rightarrow 9-10$  racks

- Option with ATCA crates < 20

Cables:

- From detectors to DAQ: 4436 optic links

- From DAQ to the control room: 374 optic links (double), max 480 links

#### In barrack

3 VME crates (1kW) 20 DAQ computers (1kW)  $\rightarrow$  3-4 racks

# Migration to ATCA (Igor Konorov 08-02-2021)

#### ATCA Carrier Card :

- 4 DHmx/DHsw modules

- 4 Optical interface AMC cards

- 16 links between A & B connectors

#### **Rear interfaces**

- 8 x Ethernet for IPBus

- USB for JTAG

- SFP+ for TCS interface + 1:8 fanout

#### **Optical Interface AMC card**

• 8 + 4 FireFly Transceivers

# **Computer input / PCI Express buffer**

- Based on commercial hardware – Nereid Kintex 7 PCI Express – Trenz FMC – SFP adapter Kintex 7 XC7K160T FBG676

- 4x PCle-Gen2 interface

- 4 GB DDR3 memory

- No dedicated TCS interface

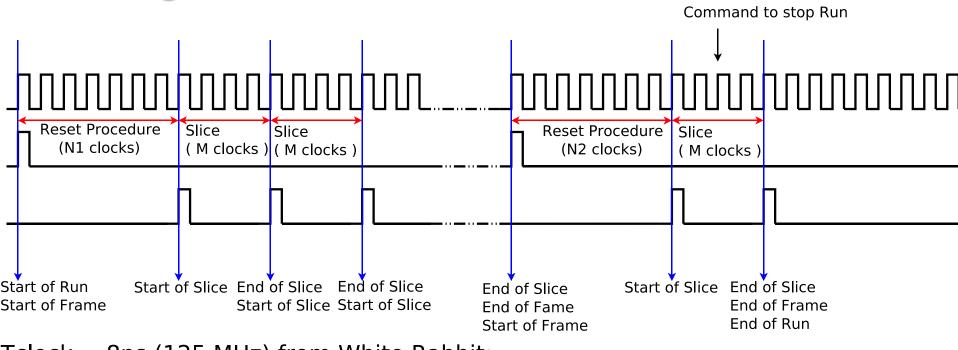

# **Time diagrams**

Tclock = 8ns (125 MHz) from White Rabbit; Reset Procedure <= 300 ms (depends on electronics);

Slice Number: 24 bits (1 us - 8.3ms) Data Size: max 16GB (real size < 160MB (20GB/s limit));

Frame: starts by Reset procedure, width 16 bits (min: 65ms, max: 549.7s), Data Size: max 1PB (real size < 10TB (20GB/s limit))

### **Data Format**

#### SPD Data Format

#### Run Structure:

| 31 | 27                                           | 23 | 19         | 15 | 11 | 7 | 3 | 0 |  |  |

|----|----------------------------------------------|----|------------|----|----|---|---|---|--|--|

|    | Start of Run                                 |    | Run Number |    |    |   |   |   |  |  |

|    | Start of Run Time in seconds since DATE      |    |            |    |    |   |   |   |  |  |

|    | Frame 0<br>Frame 1<br>Frame 2<br><br>Frame N |    |            |    |    |   |   |   |  |  |

|    | End of Run Run Number                        |    |            |    |    |   |   |   |  |  |

|    | End of Run Time in seconds since DATE        |    |            |    |    |   |   |   |  |  |

Number of Frames in the Run: 1-N, where N is maximal number of frames in the Run (assigned by TCS Controller)

#### Frame Structure:

| 31 | 27                                           | 23        | 19                        | 15 | 11 | 7         | 3      | 0 |  |  |

|----|----------------------------------------------|-----------|---------------------------|----|----|-----------|--------|---|--|--|

|    | Start of Frame                               | LSB of Ru | LSB of Run Number Frame N |    |    | ame Numbe | Number |   |  |  |

|    | Start of Frame Time in seconds since DATE    |           |                           |    |    |           |        |   |  |  |

|    | Slice 0<br>Slice 1<br>Slice 2<br><br>Slice K |           |                           |    |    |           |        |   |  |  |

|    | End of Frame LSB of Run Number Frame Number  |           |                           |    |    |           |        |   |  |  |

|    | End of Frame Time in seconds since DATE      |           |                           |    |    |           |        |   |  |  |

Number of Slices in the Frame: 1-K, where K is maximal number of slice in the Frame assigned by TCS Controller

#### Slice Structure:

| 31 | 27                                                               | 23 | 19           | 15 | 11 | 7 | 3 | 0 |  |  |  |

|----|------------------------------------------------------------------|----|--------------|----|----|---|---|---|--|--|--|

|    | Start of Slice                                                   |    | Slice Number |    |    |   |   |   |  |  |  |

|    | LSB of Run Number Frame Number                                   |    |              |    |    |   |   |   |  |  |  |

|    | Data Block 0<br>Data Block 1<br>Data Block 2<br><br>Data Block X |    |              |    |    |   |   |   |  |  |  |

|    | End of Slice Slice Number                                        |    |              |    |    |   |   |   |  |  |  |

|    | Total size of all data blocks in 32-bits words                   |    |              |    |    |   |   |   |  |  |  |

Number of Blocks in the Slice depends on DAQ configuration and data flux.

#### Data Block Structure of High Level Data Concentrators (Switches, Multiplexers etc.):

| 31                                          | 27                                                                                                                                                     | 23 | 19 | 15 | 11 | 7 | 3 | 0 |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|---|---|---|--|--|

| Block Size in 32-bits words                 |                                                                                                                                                        |    |    |    |    |   |   |   |  |  |

| Version Reserved Block Type Concentrator ID |                                                                                                                                                        |    |    |    |    |   |   |   |  |  |

| Frame Number Slice Number                   |                                                                                                                                                        |    |    |    |    |   |   |   |  |  |

|                                             | Data blocks from low level Data Concentrators<br>with the same data structure or<br>physical data from FE electronics for lowest<br>Data Concentrators |    |    |    |    |   |   |   |  |  |

|                                             | Checksum                                                                                                                                               |    |    |    |    |   |   |   |  |  |

#### Data Block Structure of Lowest Level Data Concentrators (FE Concentrators):

| 31                                                                                                                   | 27       | 23    | 19     | 15              | 11   | 7 | 3 | 0 |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-------|--------|-----------------|------|---|---|---|--|--|

| Block Size in 32-bits words                                                                                          |          |       |        |                 |      |   |   |   |  |  |

| Version                                                                                                              | Reserved | Block | < Туре | Concentrator ID |      |   |   |   |  |  |

| Frame                                                                                                                | Number   |       |        | Slice Nur       | nber |   |   |   |  |  |

| Physical Data from port 0<br>Physical Data from port 1<br>Physical Data from port 2<br><br>Physical Data from port Z |          |       |        |                 |      |   |   |   |  |  |

|                                                                                                                      | Checksum |       |        |                 |      |   |   |   |  |  |

Number of ports depends on FE Data Concentrator Type. For instance, Igor Konorov ifTDC Multiplexer has 15 input ports.

### **Status**

- AMBER/NA64 DAQ is scheduled to start to start 2-3 year before SPD. Its current status allows us to consider it as the good developed and tested prototype for SPD at the level of CDR.

- AMBER/NA64 DAQ consists of dedicated modules of 3 types only: two types of Data Handling multiplexer (DHmx and UDHmx), and Time Control System (TCS).

- We already have in Dubna 2 DHmx multiplexers and TCS module. That is enough for testing of Straw Tracker modules ONLY.

### **Problems**

- We need to formalize our relations with developers of AMBER/NA64 DAQ modules from Technische Universität of München (TUM). In the best case they should join SPD collaboration in some way. In the worst case we need to find a group which will support these modules with a help of the TUM developers, or develop their own compatible modules.

- We start negotiation with a group from St.Petersburg Polytechnic University (SPbPU) as the candidate for such group. SPD relation with this group need to be formalized. The problem of technical documentation transfer form TUM to SPD and SPbPU becomes very actual.

# Silicon Vertex Detector Front-end electronics

25.03.2021

# Relevant FEE DAQ numbers

| # layer                           | 1 (MAPS)       | 2 (MAPS)       | 3 (MAPS)       | 4 (DSSD) | 5 (DSSD) | Total                                     |

|-----------------------------------|----------------|----------------|----------------|----------|----------|-------------------------------------------|

| Sensor numbers<br>/layer          | 448            | 840            | 1736           | 228      | 368      | <mark>596(DSSD)</mark><br>+<br>3024(MAPS) |

| Ladder numbers                    | 11             | 20             | 28             | 19       | 23       | 101                                       |

| Sensor numbers<br>/stave (module) | 28             | 28             | 28             | 2        | 2        |                                           |

| Numbers stave<br>(modules)/layer  | 16             | 30             | 62             | 114      | 184      |                                           |

| Numbers e-<br>links/stave         | 8              | 8              | 8              |          |          |                                           |

| Numbers analog<br>MUX-OUT/module  |                |                |                | 10       | 10       |                                           |

| Read-out channels<br>/ layer      | 128<br>e-links | 240<br>e-links | 496<br>e-links | 1140     | 1840     | 864 e-links +<br>2980 analog<br>MUX-OUT   |

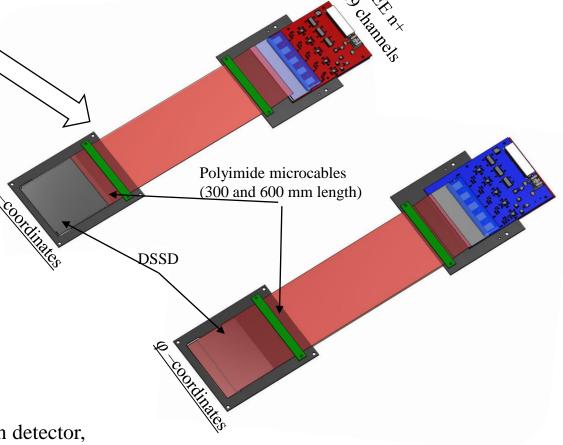

# Current SPD Si module prototype

#### BM@N Si-Module

#### DSSD parameters:

- Size: 63x63x0.3 mm<sup>3</sup> (on 4" FZ-Si wafers)

- Topology: double side microstrip (DSSD) (DC coupling)

- Pitch p<sup>+</sup> strips: 95 μm;

- Pitch n<sup>+</sup> strips 103 μm;

- Stereo angle between  $p^+/n^+$  strips:  $2.5^0$

- Number of strips:  $640 (p^+) \times 614(n^+)$

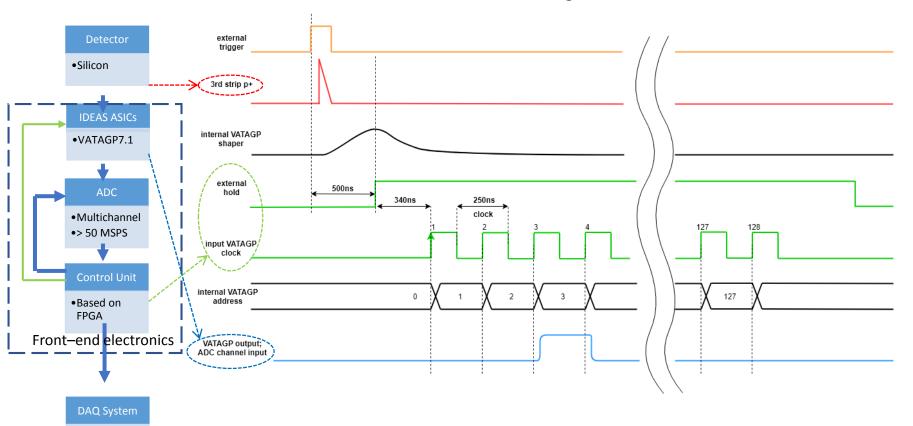

The module consists of one silicon detector, glued to the frame and connected with front-end electronics via thin polyimide cable. FEE based on VATAGP7.1 ASICs

#### Parameters of read-out chips

|                                                             | ASIC VATAGP7.1     |

|-------------------------------------------------------------|--------------------|

| Number of CSA                                               | 128 channels       |

| Input charges (dynamic range)                               | ±30 fC             |

| Peaking time (slow shaper)                                  | 500 ns (typ.)      |

| Peaking time (fast shaper)                                  | 50 ns              |

| Noise (ENC)                                                 | 70e +12e/pF (typ.) |

| Lowest threshold (no capacitance)                           | 0.12 fC            |

| Voltage supply                                              | +1.5V, -2.0 V      |

| Gain from input to output buffer<br>(diff. output currents) | 16.5 µA/fC         |

| Output Serial analog<br>multiplexer clock speed             | 3.9 MHz            |

| Power dissipation per channel                               | 2.2 mW             |

#### Serial read-out diagram

#### Possible solutions for ASIC read-out

| ASIC                 | APV25                                    | VATAGP7.3                               | n-XYTER                                  | TIGER                          | ToASt                               |

|----------------------|------------------------------------------|-----------------------------------------|------------------------------------------|--------------------------------|-------------------------------------|

| Channels<br>number   | 128                                      | 128                                     | 128                                      | 64                             | 64                                  |

| Dynamic Range        | -40fC ÷ 40fC                             | -30fC ÷ 30fC                            | Input current<br>10nA<br>Polarity - and+ | 1÷50fC                         | 1÷40fC                              |

| Gain                 | 25mV/fC                                  | 20µA/fC                                 | 59.4 mV/fC                               | 10.35mV/fc                     | ToT gain<br>40ns/fC                 |

| Noise                | 246e <sup>-</sup> +36 e <sup>-</sup> /pF | 70e <sup>-</sup> +12 e <sup>-</sup> /pF | 900e <sup>-</sup> at 30pF                | 2000e <sup>-</sup> at<br>100pF | 1500e <sup>-</sup>                  |

| Peaking time         | 50ns                                     | 50ns/500ns                              | 30ns/ 280ns                              | 60ns/ 170ns                    | 50 / ≥ 100ns                        |

| Power<br>consumption | 1.15mW/ch.                               | 2.18mW/ch.                              | 10mW/ch.                                 | 12mW/ch.                       | 4mW/ch.                             |

| ADC                  | No                                       | No                                      | 16fC, 5 bit                              | 10-bit<br>Wilkinson ADC        | 8 bit                               |

| TDC                  | No                                       | No                                      | Timestamp<br>resolution <<br>3.125ns     | Timestamp<br>resolution < 5ns  | Timestamp<br>resolution <<br>6.25ns |

- Optimal choice of DSSD module ASIC should be done after ongoing R&D

- Choice of MAPS detector is not done.

## Straw tracker

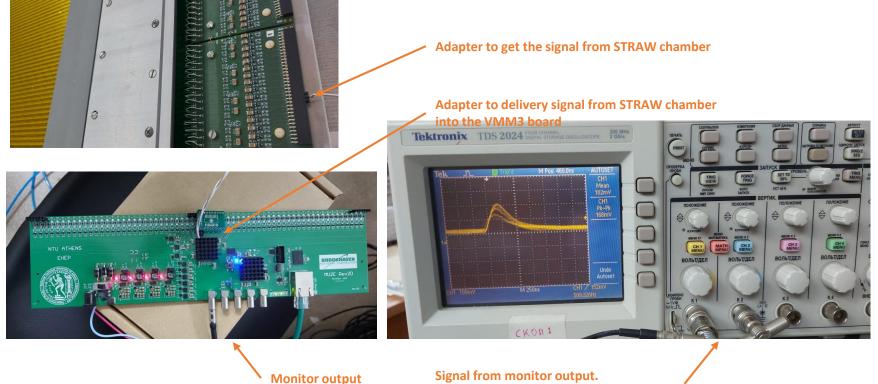

# Signals from STRAW chambers with <sup>55</sup>Fe

## Straw tracker. iFTDC

I.Konorov developed so-called "iFTDC" which is a TDC module built using FPGA chip.

iFTDC can work both in triggered or triggerless mode (this has been tested and confirmed), has precision down to 150 ps: well above the requirements of the straw tracker.

#### 5 card of iFTDC now is used for tests.

Straw tracker group is studying also other options for FEE.

#### **iFTDC**

#### Specification

- ARTIX7 FPGA XC7A-35

- 64 channels,

- Programmable signal edge or both edges

- Bin size : 1 ns, 0.5 ns, 0.25 ns (32 channels)

- Time resolution : 300ps, 170 ps, 10 ps

- Differential nonlinearity : 10%, 20%, 40%

- Trigger less capable data flow

#### Applications

- MWPC(tested), Drift Chambers

- Scintillation Counters with limited requirements for time resolution

### TRACKER ELECTRONICS DUNA

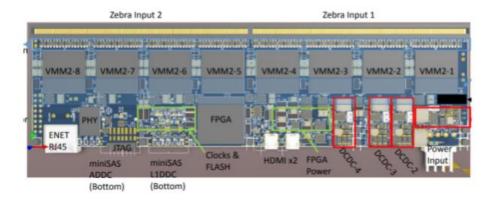

Figure 5: MMFE-8 readout board implements 8 VMM ASICs, equivalent to 512 channels, in a board with dimensions  $215mm \ge 60mm \ge 2.54mm$ .

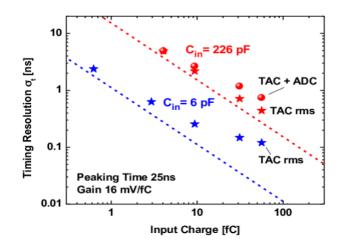

Figure 4: VMM3a time resolution as a function of input charge. Better than us time resolution is obtained for suitably large deposited charge signals. [4]

### VMM3 Meets STT Readout Requirements

#### VMM3 Time Resolution Readout requirements: · Measure deposited charge & time t; ---- 200pF, 200ns solid line: theor. 200pF, 25ns Timing resolution << 1ns;</li> symbols: measured 200pF, 100ns . Low threshold: charge from single ion pair; nominal gain 9mV/fC -- A-- 200pF, 50ns 10n • Dynamic range > 1000 on charge; Timing resolution, time walk [s] timing ramp 125ns -- -- 200pF, 25ns · Max width of readout board: 5cm; -- 8-- 2pF, 25ns \* Max length of readout board: 16 cm every 64 channels for double readout time walk 200pF, 25ns 1n VMM3 satisfies required <1ns timing Measures Q + T for each input Built-in pulser for accurate electronic response calibration 100p V 1.0 0.2 0.4 0.6 0.8 0.0 Compact 64-ch ASIC well suited to tight spatial constraints

G. lakovidis, BNL

# ECAL Front End Readout

Front End electronic for SPD ECAL based of:

- 1. ADC-64 14 bit digitizer, 64 MHz 64 channels

- 2. 16 channels Front END card with Power control for SiPms

- 3. 16 SiPM board + 1 Temperature sensor

### Current version used for tests!!!

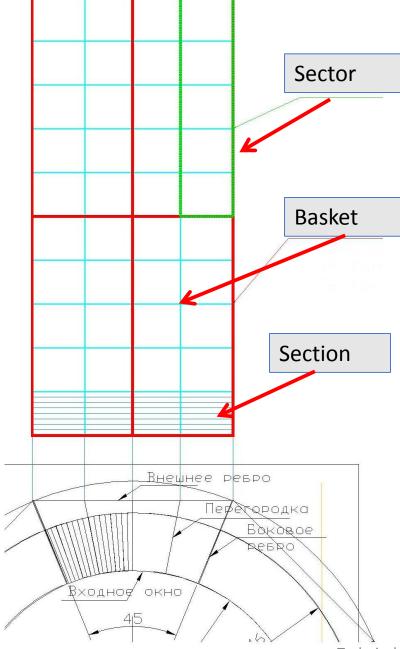

One Sector = 1/8 ECAL The Frame divided on 8 Sectors

Each sector has 4 Gaskets Each Gasket has 10 Sections One Sector – consist of 64 cells 64 cells readout of one ADC-64

ADC-64 Numbers for: One Sector = 40 One Barrel of 8 Sect.= 40x8=320 Two End Cups = 75x2=150

N\_Front\_End\_Card=4 x N\_ADC

#### 64 channel Wave form digitizer Specially designed for ECAL ADC\_64Ecal – <u>https://afi-project.jinr.ru/projects/adc64ecal/wiki</u>

- 1. 64 MHz samples frequency

- 2. 14 bit/per sample

- White Rabbit provides subnanosecond synchronization accuracy

- 4. Zero suppression mode

- Can operate in Streamer mode

Trigger less DAQ

- 6. Water cooling

- 7. Can operate in Magnetic Field

- 8. Power : ~ 50 Wt.

- 9. Total heating: 470\*50=23.5kW

# Muon (Range) System Front-End Electronics (analog & digital, FPGA-based)

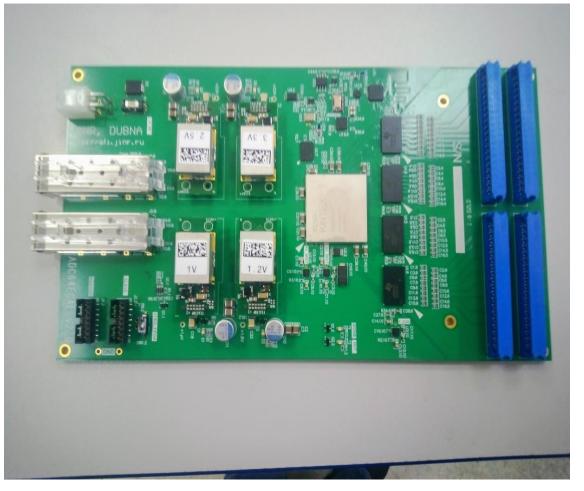

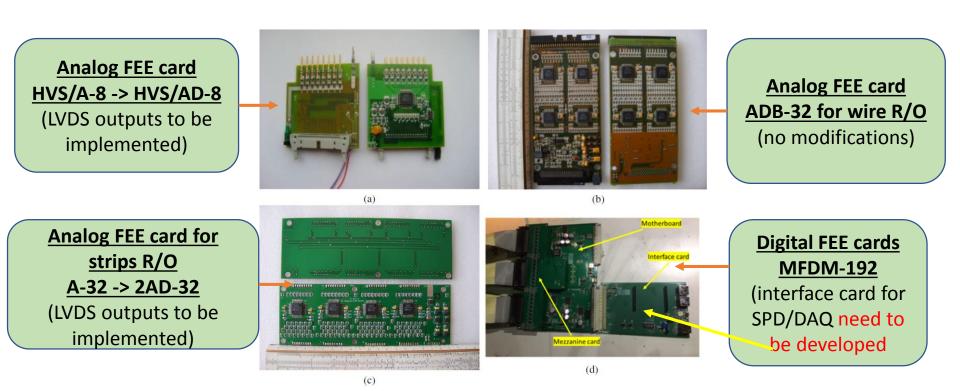

#### Main FEE prototype cards

#### (for test in BTZ)

**FE electronics of SPD RS** (analog and digital) Alekseev G., 25.03.2021

- Analog electronics based on two 8-channel chips: Ampl-8.3 и Disk-8.3, used in D0/FNAL и COMPASS/CERN

- It is paled to replace by: Ampl-8.51, Ampl-8.11R (will be ready by end of 2021) и Disk-8.15 (ready)

- **Digital electronics** based on FPGA chip Xilinx/Artix7. 192-channel VME units was developed and have been ordered (7pcs) for readout wires and strips (totally 1344 channels) from RS prototype (delivery autumn 2021.)

- **RS Prototype test at Nuclotron** is fully covered with existing FEE. Analog cards ADB-32 should be delivered from CERN during this summer. The digital VME unit MFDM-192 need to be tested in the ideal case in autumn/winter 2021.

## **Front-End electronics summary**

- Silicon vertex detector TDC/ADC: few promising options is developing for PANDA and ALICE front-end electronics. No final decision yet.

- Electromagnetic calorimeter (SiPMs) ADC: No final decision yet.

- Straw tracker: iFTDC developed for COMPASS, NA64 is planned for SPD or VMM3 based TDC/ADC.

- Range system TDC: The SPD range system closely follows the design of the range system of PANDA, which is in a well-advanced state. The digital part of the PANDA front-end electronics is very closed to what we want for the SPD-DAQ.

# **SPD DCS & BTZ**

**29.04.2021** Tow talks:

- SPD detector control system and Beam Test Zone, A. Chepurnov & D. Gribkov, SINP MSU: WinCC Open Architecture

- DCS of the miniSPD, Kirill Salamatin & Temur Enik, JINR: Tango

# **DCS very short summery**

#### Tango:

- + free system with open code

- + widely used in JINR

- + implemented at miniSPD

#### WinCC OA:

- + commercial system Simatic

- + standard for CERN

- + under consideration as standard for JINR !!!

- + gateway for Tango

- + will be implemented for RS in SPD beam test zone

- high price of the system and stuff education

- still not widely used in JINR

# Thank you for attention