## Vertex Detector SPD

**B.** Topko behalf Vertex Detector SPD team

SPD collaboration meeting

10 June 2021

- Performance requirements of the Vertex Detector (VD)

- VD general layout

- MAPS based layers

- DSSD based layers

- DSSD module layout

- DSSD module prototype

- Summary

#### Performance requirements of the Vertex Detector

From general conditions:

Close to  $4\pi$  geometry;

Number of coordinate layers: ;

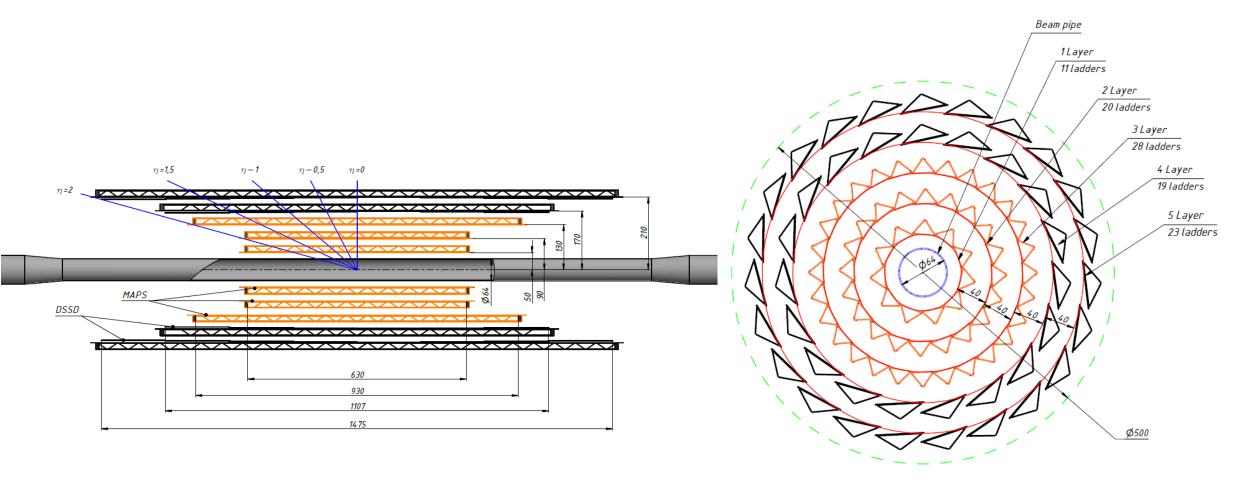

Vertex Detector (Version-1, CDR) based on two types Si-sensors

- Double Side Silicon Detector (DSSD) outer 2 layers;

- MAPS (Monolitic Active Pixel Sensor) inner 3 layers

Material budget of 1 layer DSSD include:

- Si (300  $\mu$ m)= 0,003 $X_0$ ;

- Polyimide cable =  $0,0016X_0$  (1 cable) ÷  $0,0048X_0$  (3 cables);

- Carbon frame= $0,005X_0$ ;

Barrel cover up to  $|\eta| = 2$ ;

End-cap cover up to  $|\eta| = 2,5$ ;

Track reconstruction efficiency for muons >99% at p≤ 13 GeV/c (for 0≤| $\eta$ |≤2,5); Coordinates resolutions:  $\sigma_{r\varphi} < 50 \mu m$ ,  $\sigma_z < 100 \mu m$ .

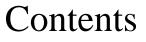

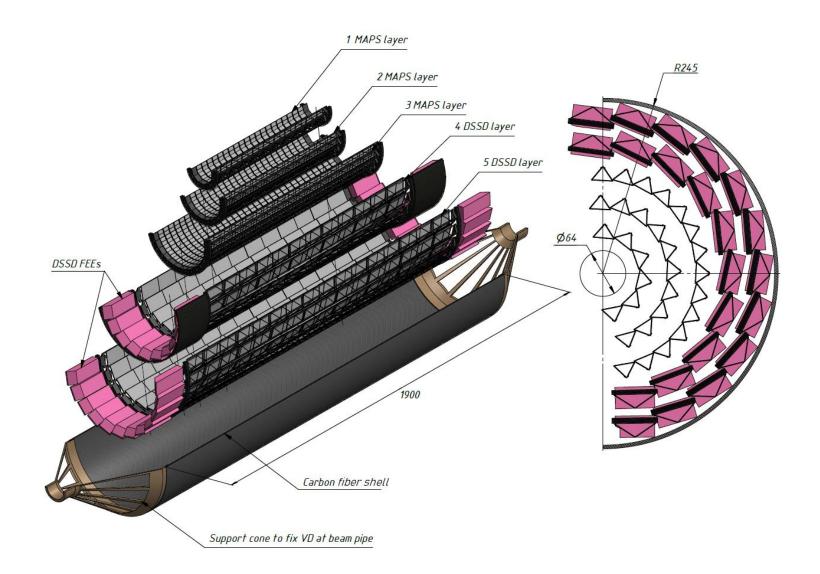

#### VD general layout

Longitudinal (left) and transversal (right) cross-sections of the DSSD+MAPS Vertex Detector barrel part

SPD collaboration meeting 10 June 2021

#### VD general layout

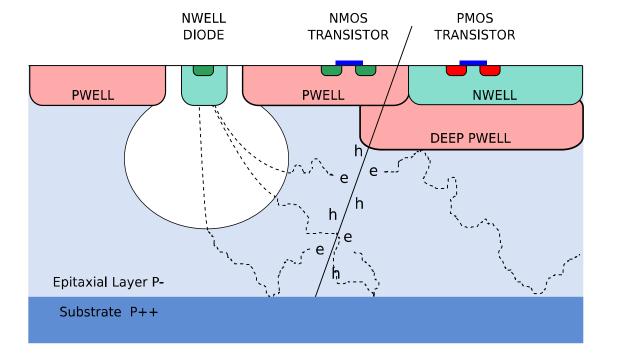

## MAPS based layers

Sensors will planned to be assembled to ladders such as ALICE outer barrel (OB) staves with two chips rows.

Schematic of MAPS pixels in imaging CMOS (left) and Schematic exploded view and cross section of the ALICE OB Stave (right) [ALICE Collaboration, TDR for the Upgrade of the ALICE Inner Tracking System Journal of Physics J. Phys. G 41 (2014) 087002]

SPD collaboration meeting 10 June 2021

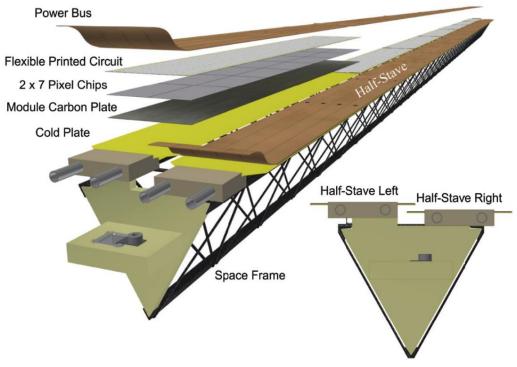

## DSSD based layers

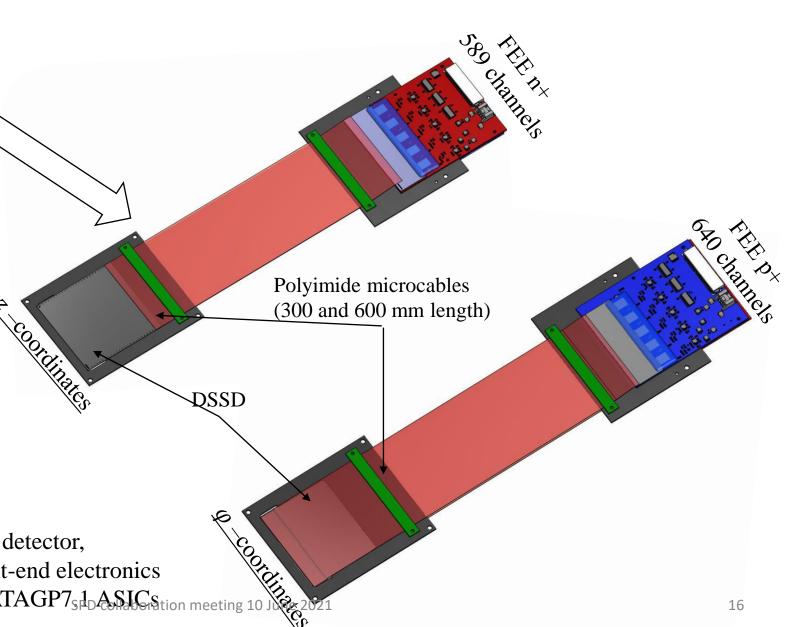

#### Barrel DSSD module concept

Barrel DSSD module 3D model

Low left corner of detector photomask p+ side (left) and n+ side (right) (ZNTC, Zelenograd, Russia)

SPD collaboration meeting 10 June 2021

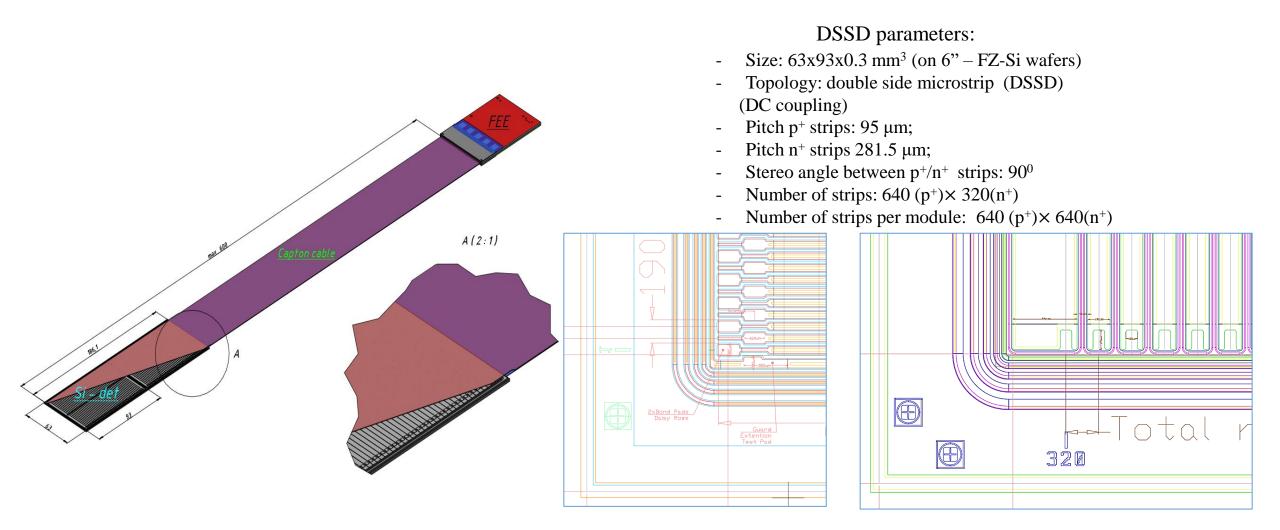

#### Low-mass microcables

Manufacturing: LED Technologies Ukraine. Ukraine, Kharkiv viatcheslav.borshchov@cern.ch, maksym.protsenko@cern.ch

#### Maximum cable length 600 mm

## Possible solutions for ASIC read-out

| ASIC                 | APV25                                    | VATAGP7.3                               | n-XYTER                                  | TIGER                         | ToASt                               |

|----------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-------------------------------|-------------------------------------|

| Channels<br>number   | 128                                      | 128                                     | 128                                      | 64                            | 64                                  |

| Dynamic Range        | -40fC ÷ 40fC                             | -30fC ÷ 30fC                            | Input current<br>10nA<br>Polarity - and+ | 1÷50fC                        | 1÷40fC                              |

| Gain                 | 25mV/fC                                  | 20μA/fC                                 | 59.4 mV/fC                               | 10.35mV/fc                    | ToT gain 40ns/fC                    |

| Noise                | 246e <sup>-</sup> +36 e <sup>-</sup> /pF | 70e <sup>-</sup> +12 e <sup>-</sup> /pF | 900e <sup>-</sup> at 30pF                | 2000e <sup>-</sup> at 100pF   | 1500e <sup>-</sup>                  |

| Peaking time         | 50ns                                     | 50ns/500ns                              | 30ns/ 280ns                              | 60ns/ 170ns                   | 50 / ≥ 100ns                        |

| Power<br>consumption | 1.15mW/ch.                               | 2.18mW/ch.                              | 10mW/ch.                                 | 12mW/ch.                      | 4mW/ch.                             |

| ADC                  | No                                       | No                                      | 16fC, 5 bit                              | 10-bit Wilkinson<br>ADC       | 8 bit                               |

| TDC                  | No                                       | No                                      | Timestamp<br>resolution <<br>3.125ns     | Timestamp<br>resolution < 5ns | Timestamp<br>resolution <<br>6.25ns |

| TIG                    | ER ASIC specification | → <u>ToASt ASIC specification</u> |

|------------------------|-----------------------|-----------------------------------|

| Parameter              | Value                 | Value                             |

| Number of<br>channels  | 64                    | 64                                |

| Input dynamic<br>range | 2-50 fC               | 1-40 fC                           |

| Input<br>capacitance   | up to 100 pF          | 2-17 pF                           |

| ENC                    | < 2000 e⁻             | 1500 e⁻                           |

| Maximum event<br>rate  | 60 kHz/channel        | 40 kHz/channel                    |

| Serial links           | 4                     | 2                                 |

| Pads position          | around the chip       | on two sides only                 |

| Trigger-less           | $\checkmark$          | $\checkmark$                      |

| Power<br>consumption   | 10-12 mW/channel      | 4 mW/channel                      |

ToASt ASIC advantages:

- ✓ not necessary to be redesigned – ASICs could be placed on PCB tighter;

- ✓ based on simulations input dynamic range is up to 50 fC;

- ✓ available at the beginning of next year.

\*based on discussions with Maxim Alexeev (INFN, Torino)

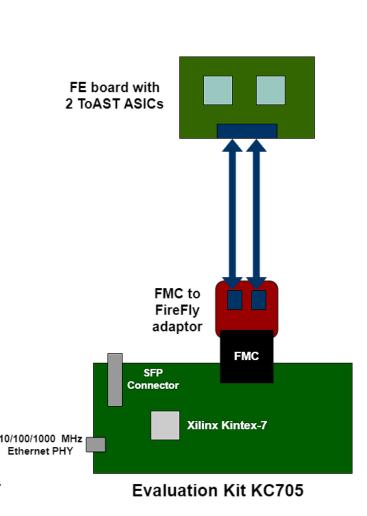

## FEE ASIC R&D

FEE ToAST tests are foreseen at the beginning of next year

#### *First stage:*

Test preparation scenario:

- design PCB for 2 ToAST ASICs (*in JINR*);

- Wire bonding (*in Torino / JINR*);

- FPGA design for slow control and data acquisition *(in JINR)*;

- PC application to send ASIC settings and analyze data (*in JINR*);

- Run tests in JINR.

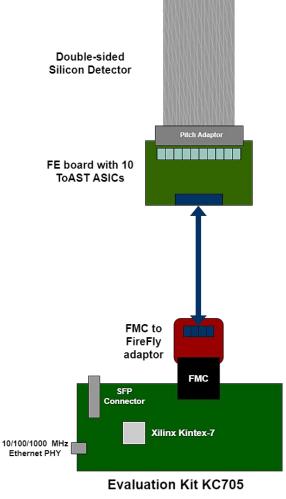

#### Test preparation scenario:

Second stage:

- design PCB for 10 ToAST ASICs (*in JINR*);

- Wire bonding ToAST to Pitch Adapter (*in Torino / JINR*);

- Wire bonding FEE board to DSSD (in *JINR*);

- Run tests in JINR.

\*based on discussions with Maxim Alexeev (INFN, Torino)

## Relevant VD SPD numbers

| Parameter                                | Layer 1<br>(MAPS) | Layer 2<br>(MAPS) | Layer 3<br>(MAPS) | Layer 4<br>(DSSD)         | Layer 5<br>(DSSD)         | Total for<br>layer 1,2,3 | Total for<br>layer 4,5 | Total                                      |

|------------------------------------------|-------------------|-------------------|-------------------|---------------------------|---------------------------|--------------------------|------------------------|--------------------------------------------|

| N <sub>MAPS</sub> /mod                   | 1                 | 1                 | 1                 | 0                         | 0                         | -                        | -                      | -                                          |

| N <sub>DSSD</sub> /mod                   | 0                 | 0                 | 0                 | 2                         | 2                         | -                        | -                      | -                                          |

| R <sub>layer</sub> , mm                  | 50                | 90                | 130               | 170                       | 210                       | -                        | -                      | -                                          |

| L <sub>layer</sub> , mm                  | 600               | 630               | 930               | 1107                      | 1475                      | -                        | -                      | -                                          |

| N <sub>ladders</sub> /layer              | 11                | 20                | 28                | 19                        | 23                        | 59                       | 42                     | 101                                        |

| N <sub>MAPS</sub> /layer                 | 448               | 840               | 1736              | 0                         | 0                         | 3024                     | 0                      | 3024                                       |

| N <sub>DSSD</sub> /layer                 | 0                 | 0                 | 0                 | 228                       | 368                       | 0                        | 596                    | 596                                        |

| N <sub>ASIC</sub> /mod                   | 0                 | 0                 | 0                 | 10                        | 10                        | -                        | -                      | -                                          |

| N <sub>ASIC</sub> /layer                 | 0                 | 0                 | 0                 | 1140                      | 1840                      | -                        | 2980                   | 2980                                       |

| N <sub>read-out channel</sub> /<br>layer | 128<br>e-links    | 240<br>e-links    | 496<br>e-links    | 1140<br>analog<br>MUX-OUT | 1840<br>analog<br>MUX-OUT | 864 e-links              | 2980 analog<br>MUX-OUT | 864 e-links<br>+<br>2980 analog<br>MUX-OUT |

| S <sub>active</sub> , m <sup>2</sup>     | 0.20              | 0.38              | 0.78              | 1,34                      | 2.16                      | 1.36                     | 3.5                    | 4.86                                       |

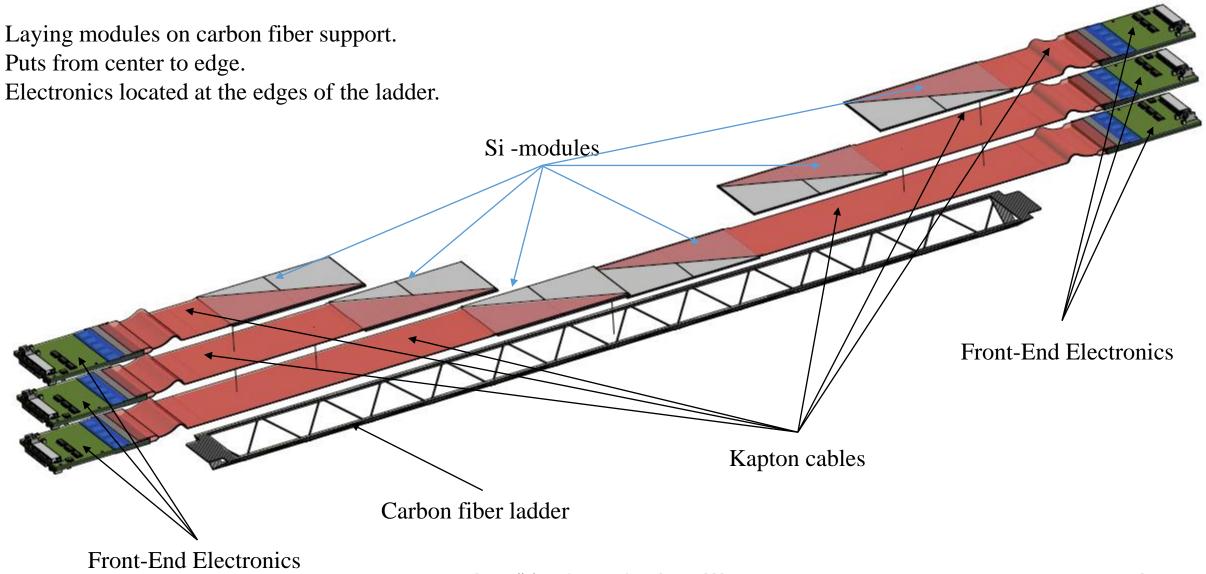

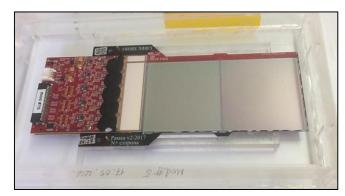

## Barrel DSSD module prototype

From general conditions of SPD facility it's necessary to minimize material budget over the track paths. That's why the main goal of prototype is to study possibility of production double-sided silicon strip detector (DSSD) module which connects to front-end electronics via thin low-mass microcables and test it for satisfaction m.i.ps detection (noise, cross-talks, common noise).

## Barrel DSSD module prototype

#### BM@N Si-Module

DSSD parameters:

- Size: 63x63x0.3 mm<sup>3</sup> (on 4" FZ-Si wafers)

- Topology: double side microstrip (DSSD) (DC coupling)

- Pitch p<sup>+</sup> strips: 95 μm;

- Pitch n<sup>+</sup> strips 103 μm;

- Stereo angle between  $p^+/n^+$  strips: 2.5<sup>0</sup>

- Number of strips:  $640 (p^+) \times 614(n^+)$

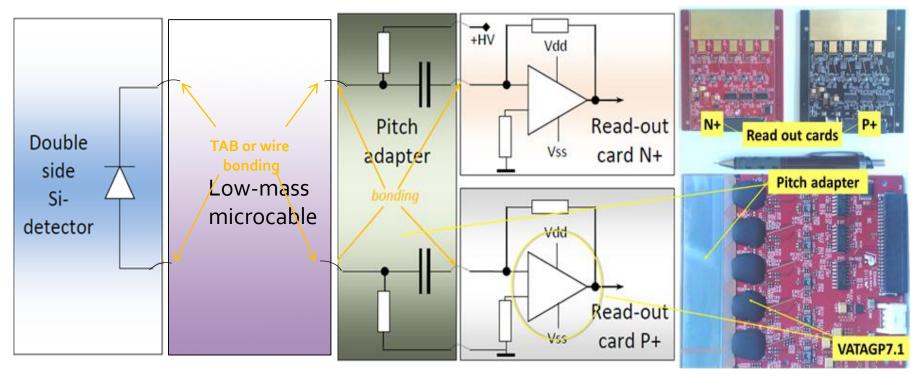

The module consists of one silicon detector, glued to the frame and connected with front-end electronics via thin polyimide cable. FEE based on VATAGP7<sub>S1D</sub>ASICS<sub>tion meeting 10</sub>

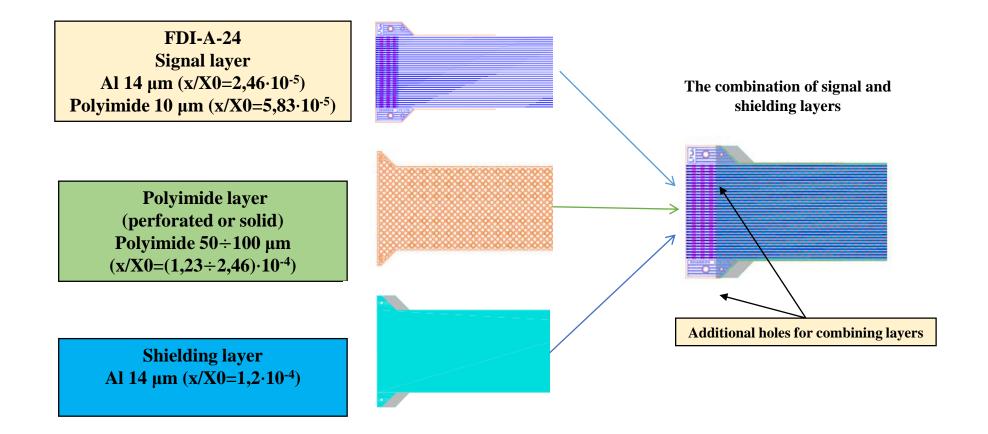

## Low-mass microcables for prototype

Manufacturing: LED Technologies Ukraine. Ukraine, Kharkiv viatcheslav.borshchov@cern.ch, maksym.protsenko@cern.ch

4 different cable topologies had been developed for DSSD barrel module prototype:

➤ «SPD-600-1»

Cable length is 600 mm. Signal layer consists of 1 conductive layer with meshed gaskets SPD-P-600-1 (for p+ side), SPD-N-600-1 (for n+ side) + 2 shielding layers;

➤ «SPD-300-1»

Cable length is 300 mm. Signal layer consists of 1 conductive layer with meshed gaskets SPD-P-600-1 (for p+ side), SPD-N-600-1 (for n+ side) + 2 shielding layers;

➤ «SPD-600-2»

Cable length is 600 mm. Signal layer is splitted to 2 conductive layers with meshed gaskets SPD-P-600-2-bot, SPD-P-600-2-top, SPD-N-600-2-bot, SPD-N-600-2-top + 2 shielding layers;

#### ➤ «SPD-300-2»

Cable length is 300 mm. Signal layer is splitted to 2 conductive layers with meshed gaskets SPD-P-600-2-bot, SPD-P-600-2-top, SPD-N-600-2-bot, SPD-N-600-2-top + 2 shielding layers; SPD collaboration meeting 10 June 2021

Photo of SPD-300-2 signal layers (n+ side) at top; Shielding layers at bottom 17

## Low-mass microcables for prototype

Manufacturing: LED Technologies Ukraine. Ukraine, Kharkiv viatcheslav.borshchov@cern.ch, maksym.protsenko@cern.ch

#### Aluminium 14-15 um Polyimide 10 um Outer signal layer Meshed polyimide 100 um (Kapton) 75 um Aluminium 14-15 um Polyimide 10 um Inner signal layer Meshed polyimide 100 um (Kapton) 75 um Polystyrene Shielding layer (Foamtak II) 165 um 190 um Aluminium 14-15 um Polyimide 10 um

#### Cable cross-section with splitted signal layer

#### Signal layer:

Conductive layer – Aluminium 14 mkm;

Insulator layer – Polyimide 10 mkm;

Meshed gasket – meshed Polyimide 75 mkm, (filling 30%).

#### Shielding layer:

Conductive layer– Aluminium 14 mkm; Insulator layer – Polyimide 10 mkm;

Gasket – Foamtak (polystyrene) 160 mkm.

## Low-mass microcables for prototype

Manufacturing: LED Technologies Ukraine. Ukraine, Kharkiv viatcheslav.borshchov@cern.ch, maksym.protsenko@cern.ch

| PD-1              |           | X0 – radiation length |                |              |

|-------------------|-----------|-----------------------|----------------|--------------|

| Layer type        | Material  | X0, mkm               | Thickness, mkm | X0, %        |

| Signal layer      | Aluminium | 87000                 | 28             | 0,032        |

| Signal layer      | Polyimide | 284000                | 20             | 0,007        |

| Signal layer(30%) | Polyimide | 284000                | 45             | 0,016        |

| Shielding layer   | Aluminium | 87000                 | 28             | 0,032        |

| Shielding layer   | Polyimide | 284000                | 20             | 0,007        |

| Shielding layer   | Foamtak   |                       |                |              |

|                   |           | То                    | tal X0, %      | 0,094        |

| PD-2              |           |                       |                |              |

| Layer type        | Material  | X0, mkm               | Thickness, mkm | <b>X0,</b> % |

| Signal layer      | Aluminium | 87000                 | 28             | 0,032        |

| Signal layer      | Polyimide | 284000                | 40             | 0,014        |

| Signal layer(30%) | Polyimide | 284000                | 90             | 0,032        |

| Shielding layer   | Aluminium | 87000                 | 28             | 0,032        |

| Shielding layer   | Polyimide | 284000                | 20             | 0,007        |

| Shielding layer   | Foamtak   |                       |                |              |

|                   |           | То                    | tal X0, %      | 0,117        |

## Pitch adapter

DSSD with DC topology doesn't contain integrated resistors and capacitors (RC), therefore external R, C are required to supply bias voltage to each strip and to electrically decouple the DC current from the electronic inputs. This role is performed by Pitch Adapter (PA) with a topology of two types for p+ and n+ sides of the detector. In addition, PA has topology of contact pads similar to chips located on the side of electronic chips. PA modules are made on sapphire plates with an epitaxial layer of silicon (SOI). Integrated poly silicon bias resistors have a value of  $0.7 - 1.0 \text{ M}\Omega$ , decoupled capacitors have a value of 140 pF. PA is assembled together with read-out ASICs on the read-out card. Positive polarity signals come from detectors to P+ read-out card (black PCB) while negative signals come to N+ read-out card (red PCB).

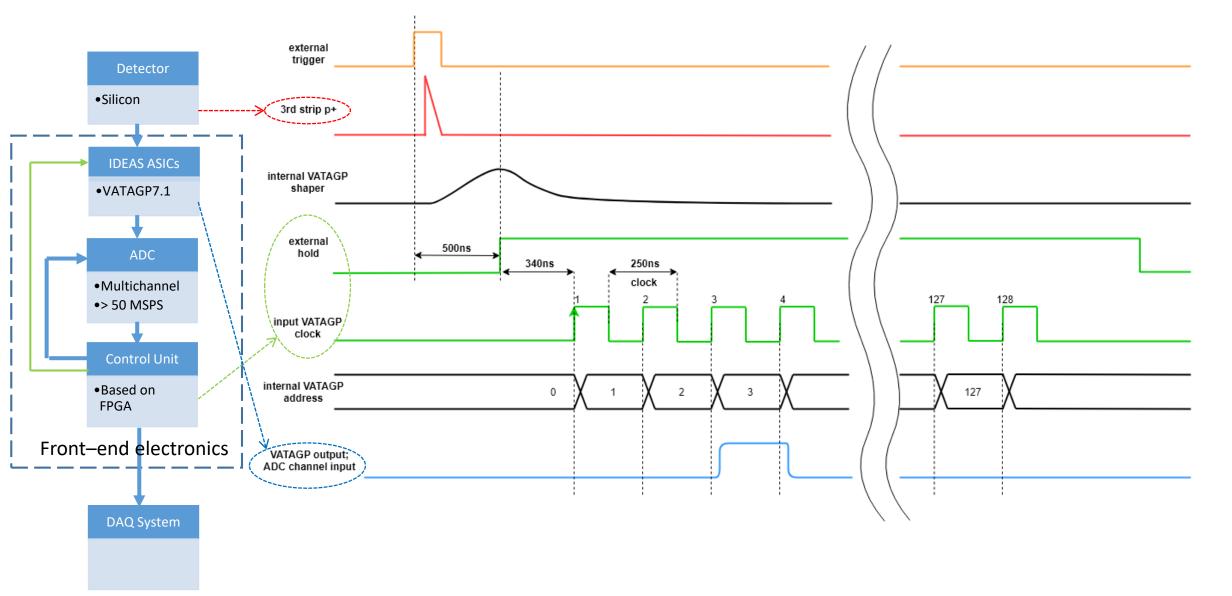

#### Serial read-out diagram

#### Summary

- First hybrid (3 MAPS layers + 2 DSSD layers) version of barrel part VD SPD conceptual design is done;

- Availability of MAPS in Russia is still open question;

- New DSSDs topology with large sensitive area 63x93 mm<sup>2</sup> is done. Detectors will be delivered at JINR till end of this year;

- At the moment DSSD FEE based on ToASt ASIC is the most promising way (tests are foreseen at the beginning of next year);

- First version of Barrel Silicon Module prototype for Vertex Detector SPD is going to be based on the BM@N modules (DSSD, 300  $\mu$ m, 2.5° stereo angle between strips, DC coupling). Now there are enough amount detectors, pitch adapters, ASICs and low-mass microcables for the prototype;

- Drawings of prototype support frames and assembly jigs in progress.

# Welcome everyone to join the Vertex Detector SPD collaboration!