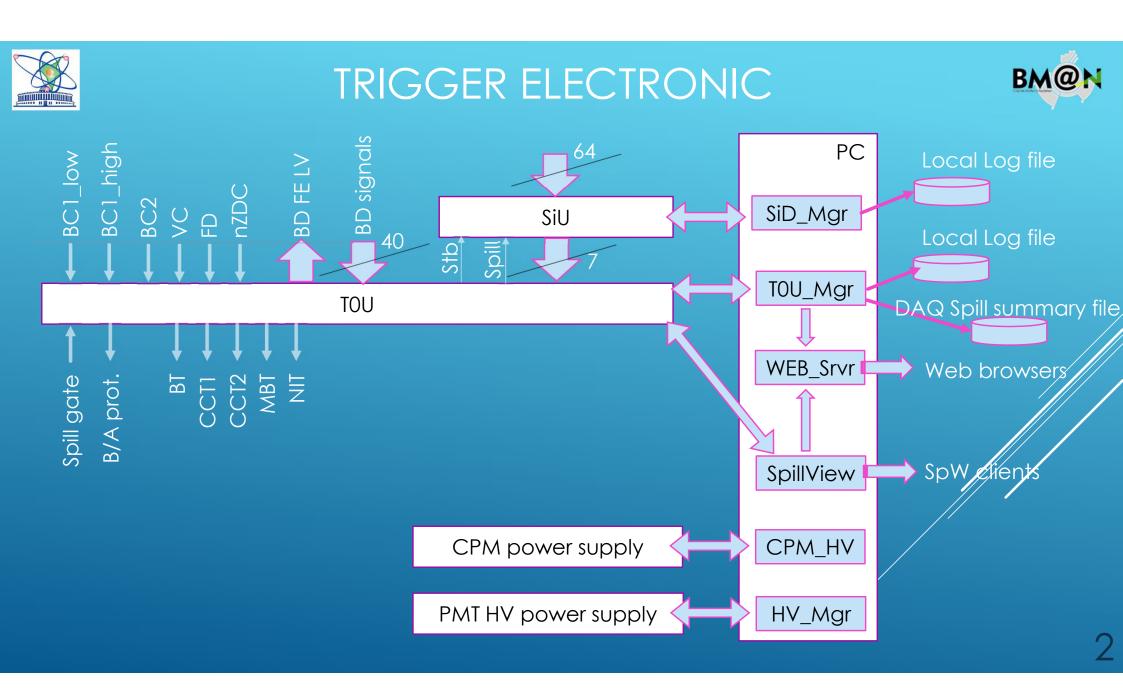

## THE TRIGGER SYSTEM ELECTRONICS

Trigger group

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SID MGR                                                                                                                                                                                                                                                                                                  |                                                                              | Channel configuration — — ×  All enabled All disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BM@N |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| GenData       Browse data       Draw data         ReadSpillNbr       XXXXXXX         Test signals to channels       All On                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Image: BM@N Silicon detector manager v.2.3         Com port       Image: Close         Com port       Image: Close         Spill operation mode       External signal         Internal generator       Manual Spill         Gate On       Spill nbr 297         Beam triggers       1390059         Data | Channel Con<br>ill start Manual Spill stop<br>a received 15.07.2022 12:58:17 | Disabled channels         0       1       2       3       4       5       6       7         Ø8       Ø9       Ø10       Ø11       Ø12       Ø13       Ø14       Ø15         Ø16       Ø17       Ø18       Ø19       Ø20       Ø21       Ø22       Ø23         Ø24       Ø25       Ø26       Ø27       Ø28       Ø29       Ø30       Ø31         Ø32       Ø33       Ø34       Ø35       Ø36       Ø37       Ø38       Ø39         Ø40       Ø41       Ø42       Ø43       Ø44       Ø45       Ø46       Ø47         Ø48       Ø49       Ø50       Ø51       Ø52       Ø53       Ø54       Ø55 |      |

| 0       1       2       3       4       5       6       7         8       9       10       11       12       13       14       15         16       17       18       19       20       21       22       23         24       25       26       27       28       29       30       31         32       33       34       35       36       37       38       39         40       41       42       43       44       45       46       47         48       49       50       51       52       53       54       55         56       57       58       59       60       61       62       63 | Counts Channel 59 Count 753386                                                                                                                                                                                                                                                                           | Multiplicity Channel 0  1.0  0.9  0.8  0.7                                   | <u>Count</u> 0 557 1 58 1 59 1 60 1 61 1 62 1 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Test mutiplisity signal in M> 3 💭<br>Channel 63 🗭 -> Test signal 0<br>Channel 62 💽 -> Test signal 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +                                                                                                                                                                                                                                                                                                        | 0.6<br>0.5<br>0.4<br>0.3<br>0.2                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3    |

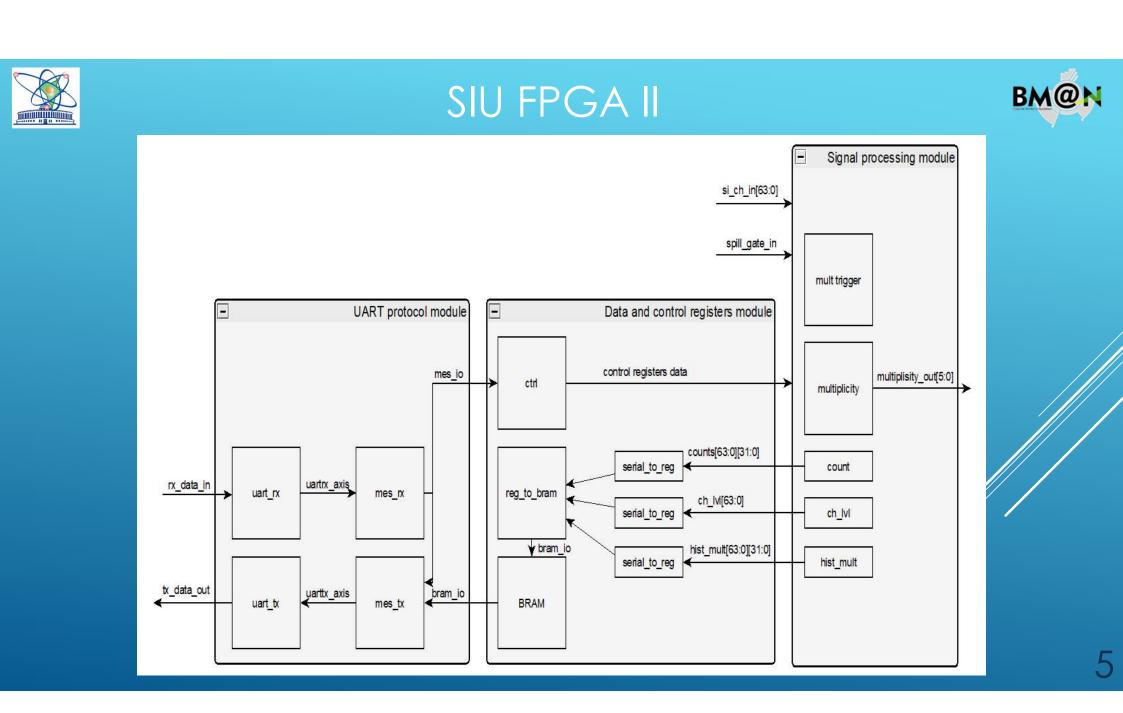

## SIU FPGA

- ▶ FPGA 5CGXBC5C6F27C7 (30000 ALMs), used 32% of FPGA ALMs

- Used Quartus Prime 19.1, programming language System Verilog

- ► Internal FPGA clock frequency 50 MHz

- Communication to PC USB virtual com-port, 115200 baud

- ▶ Compilation time ~4 min

- Project uses synchronous design. For asynchronous signals used 200 MHz digitizing frequency

- Project built using self-containing units with defined interfaces

- Project was checked with Timing Analyzer

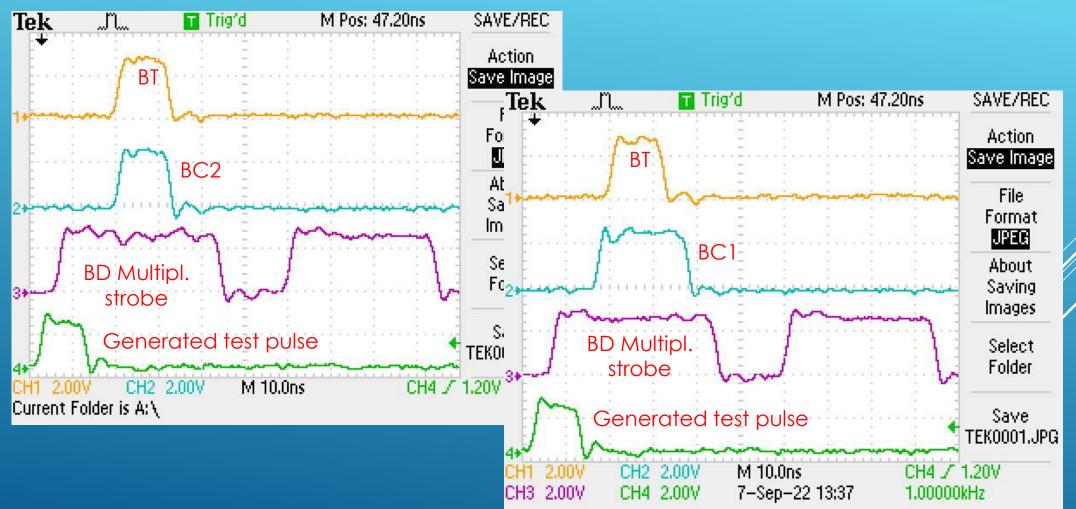

- SiU tested with the test signal generator developed for BM@N SiD and BD testing

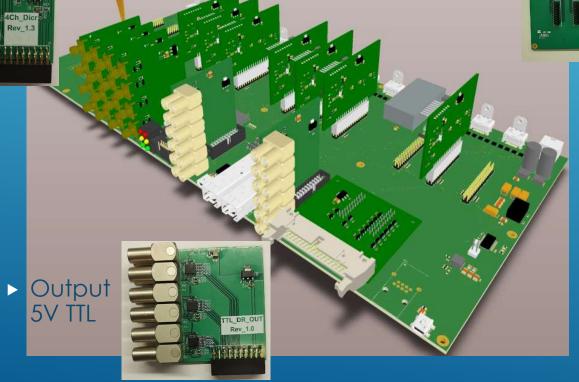

- 4-ch. Input discriminators

- ► -2 to 2V input

- ► Threshold 5mV step

- 1.5 GHz equivalent input rise time bandwidth

6

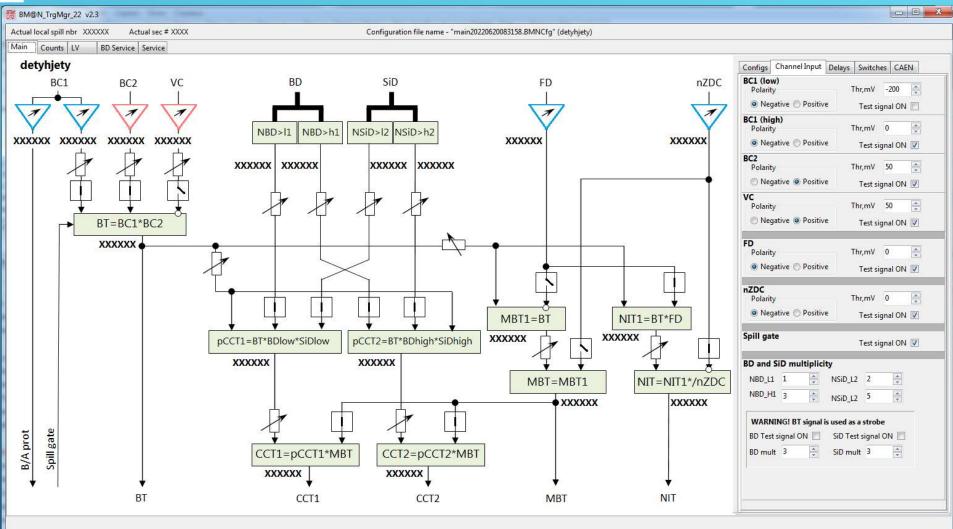

TOU

## TOU FPGA

- ► Two external Communication lines to PC USB virtual com-port, 115200 baud

- Trigger control and monitoring, both I/O. Spill data readout ~2 secs.

- ▶ Real-time counts reading for spill view server. 8 channel readout with 100 Hz, used by ~50%

- ▶ Internal communication a hybrid of I2C and SPI, written from scratch

- ► Signals

- ► 10 MHz clock

- Address flag

- MOSI

- ► MISO

- ▶ 26% FPGA ALMs used

- ▶ 7% connection lines used

- Compilation time ~7.5 min (old project ~ 12 hours)

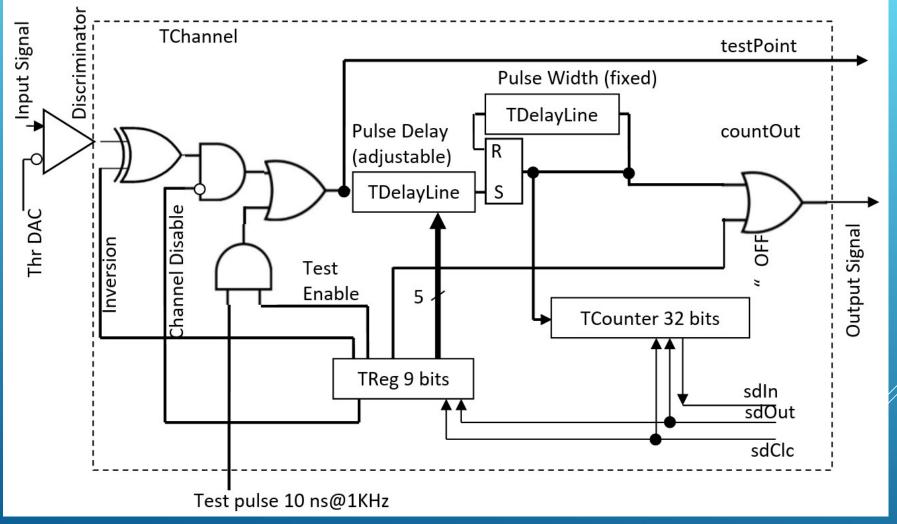

#### TOU CHANNEL I

9

## TOU CHANNEL II

- Delay lines are asynchronous for ordinary channels with short delay and synchronous for channels with long delay

- Asynchronous delay is built using FPGA element propagation delay. Very resource consuming. Not longer than 45 ns. Step ~1.5 ns.

- Synchronous delay uses FPGA 100 MHz internal clock counting therefore introduces jitter +/- 5 ns

- Synchronous delays used in circuits with delay longer than 50 ns

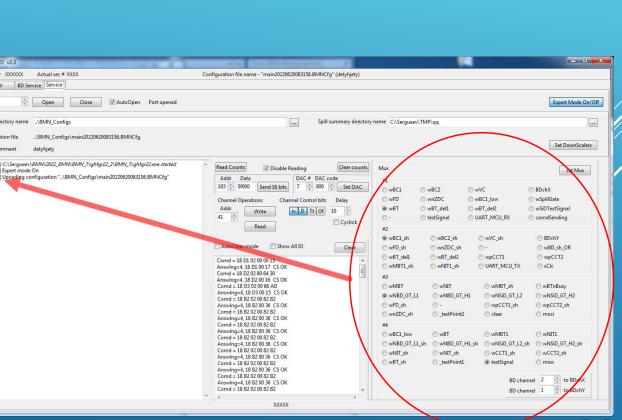

#### TOU ADJUSTMENT I

| #1            |             |       |              |       |                  |

|---------------|-------------|-------|--------------|-------|------------------|

| 🖯 wBC1 🛛 🔘    | wBC2        | © wVC |              | Ø     | BDchX            |

| 🖯 wFD 🛛 🔘     | wnZDC       | 🗇 wB  | C1_low       | O     | wSpillGate       |

| 🖲 wBT 🛛 🔘     | wBT_del1    | 🔿 wB  | T_del2       | 0     | wSiDTestSignal   |

| ð- C          | testSignal  | UA    | RT_MCU_RX    | 0     | comdSending      |

| #2            |             |       |              |       |                  |

| wBC1_sh       | 🔘 wBC2_sh   | C     | ) wVC_sh     |       | BDchY            |

| 🖱 wFD_sh      | 🔘 wnZDC_sh  | C     | 9-           |       | wBD_sh_OR        |

| 🖱 wBT_del1    | 🔘 wBT_del2  | C     | wpCCT1       |       | O wpCCT2         |

| 🔿 wMBT1_sh    | © wNIT1_sh  | C     | UART_MCU_T   | ĸ     | ⊚ sClc           |

| <b>#</b> 3    |             |       |              |       |                  |

| 🗇 wMBT        | 🖱 wNIT      |       | 🔘 wMBT_sh    |       | 🔘 wBTnBusy       |

| wNBD_GT_L1    | wNBD_GT_H   | L     | 🕐 wNSiD_GT_I | .2    | 🕑 wNSiD_GT_H2    |

| 🖱 wFD_sh      | © -         |       | O wpCCT1_sh  |       | 🖱 wpCCT2_sh      |

| 🔊 wnZDC_sh    | _testPoint2 |       | 🔘 clear      |       | 🔘 mosi           |

| ¥4            |             |       |              |       |                  |

| wBC1_low      | 🖱 wBT       |       | O wMBT1      |       | 🔘 wNIT1          |

| wNBD_GT_L1_st | wNBD_GT_H   | l_sh  | 🕐 wNSiD_GT_I | .2_sh | 🕑 wNSiD_GT_H2_sh |

| 🖱 wNIT_sh     | 🔘 wNIT_sh   |       | 🔘 wCCT1_sh   |       | 🖱 wCCT2_sh       |

| 🗇 wBT_sh      | _testPoint1 |       | testSignal   |       | 🔘 miso           |

#### TOU ADJUSTMENT II

BM@N

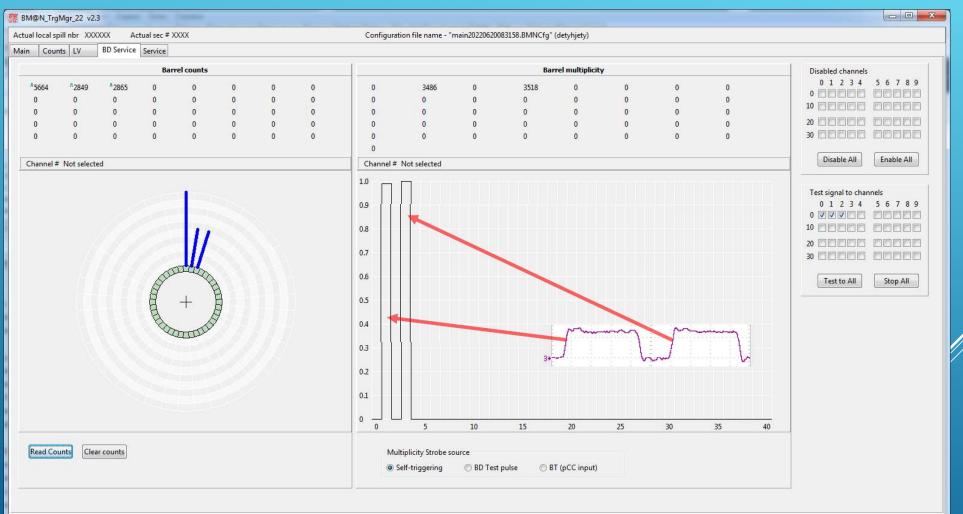

#### **BD CONTROL**

3

## ACTUAL STATE

- ► SiD module ready, passed for testing to the Silicon group

- SiD\_Mgr ready , passed for testing to the Silicon group

- TOU almost ready, needs to be tested with the input boards. Might be some cosmetics modifications will be needed

- ▶ TOU\_Mgr almost ready. Some modifications will be needed

- Web Server under development. The SRC experiment server as a template used

- Spill\_View under development. The SRC experiment server as a template used

The trigger system should be ready by the 2022 mid-October

# Thank you