# BM@N DAQ — Current Status and Development Prospects

# Alexey Shutov BM@N DAQ working group

A. Baskakov, S. Bazylev, A. Egorov, A. Fediunin, I. Filippov, S. Kuklin, A. Shchipunov, A. Shutov, I. Slepnev, V. Slepnev, N. Tarasov, A. Terletskiy

### Joint Institute for Nuclear Research

10th Collaboration Meeting of the BM@N Experiment at the NICA Facility

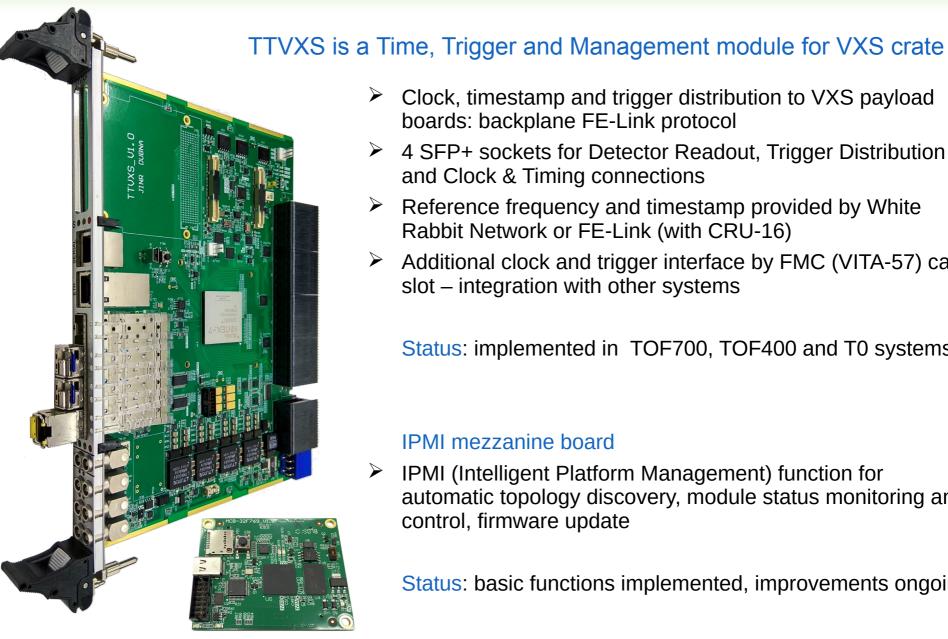

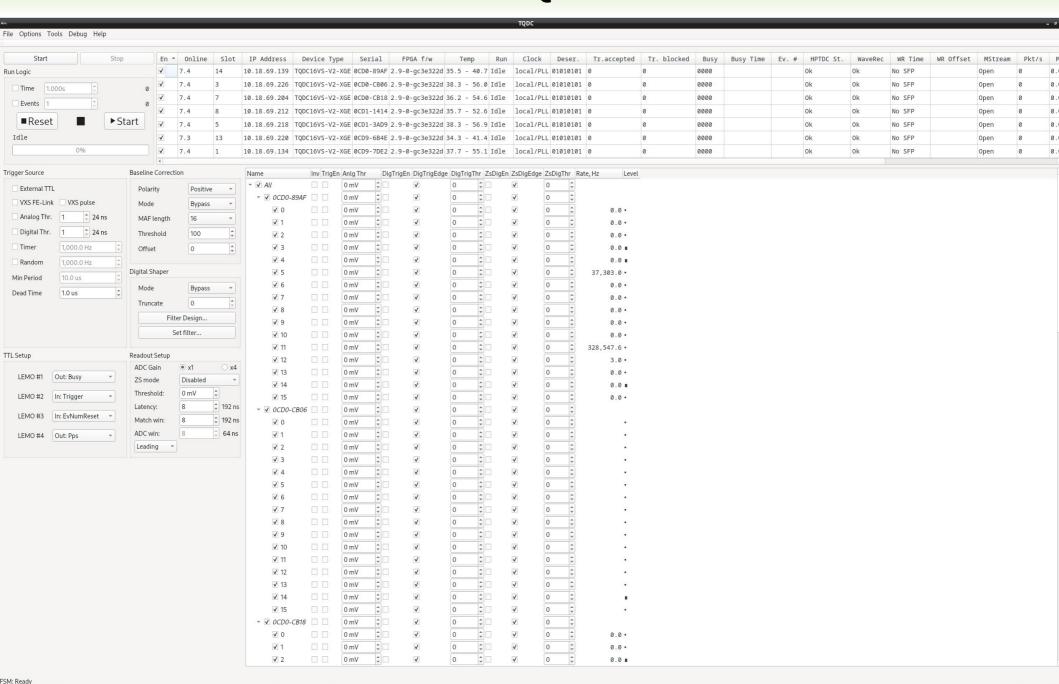

### **TTVXS**

IPMI mezzanine board

- Clock, timestamp and trigger distribution to VXS payload boards: backplane FE-Link protocol

- → 4 SFP+ sockets for Detector Readout, Trigger Distribution. and Clock & Timing connections

- Reference frequency and timestamp provided by White Rabbit Network or FE-Link (with CRU-16)

- Additional clock and trigger interface by FMC (VITA-57) card slot – integration with other systems

Status: implemented in TOF700, TOF400 and T0 systems

#### IPMI mezzanine hoard

IPMI (Intelligent Platform Management) function for automatic topology discovery, module status monitoring and control, firmware update

Status: basic functions implemented, improvements ongoing

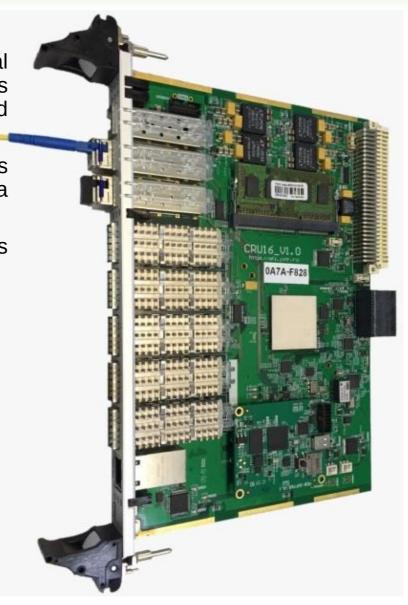

### **CRU-16**

### Common Readout Unit for 16 DRE boards

FE-Link interface to DRE boards - multi-gigabit duplex serial synchronous interconnect with deterministic latency. Provides clock and trigger information for downstream boards and receives raw data stream

4 GB SO-DIMM DDR3 memory for data buffers. Decouples realtime hardware data flow from high latency software data receivers

4 QSFP downlink sockets for 16 Detector Readout boards connections grouped by 4

- 1 QSFP uplink socket for 40 Gb Ethernet data transfer

- 3 SFP sockets for Trigger Distribution, Clock & Timing

- Management mezzanine board

- Timing synchronization by White Rabbit network

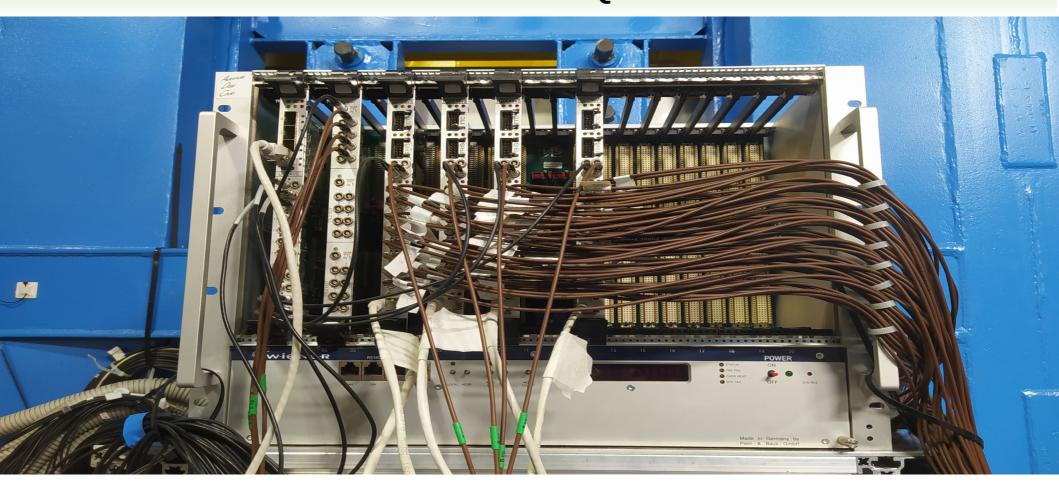

### DCH DAQ

#### **Current status:**

- ► 60 TDC64V readout modules

- TTC synchronization and trigger distribution inside one VME crate

- Last VMEDAQ readout system

### **Future plans:**

Replace by 2 CSC chambers

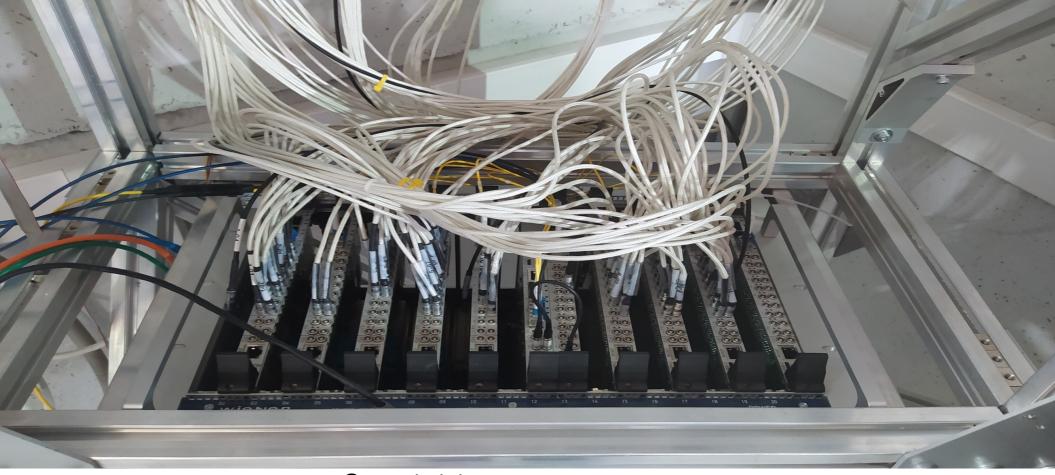

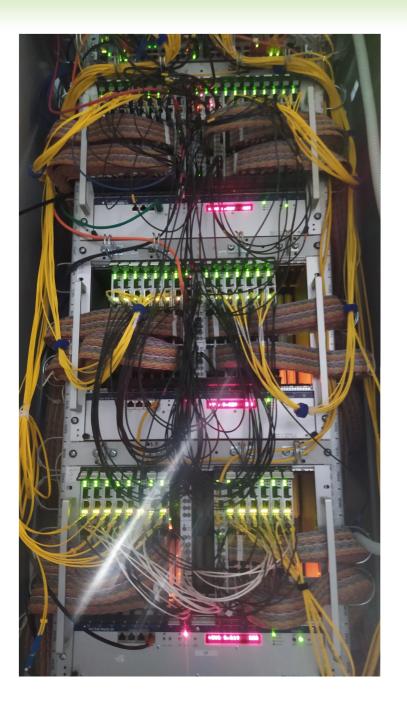

### TOF700 & TOF400 DAQ

#### **Current status:**

- > TOF700 51 TDC64VHLE readout modules

- TOF400 28 TDC72VHL readout modules

- > TTVXS time sync and trigger via backplane

- Replace VMEDAQ with 1G ethernet readout

### **Future plans:**

Add 1 VXS crate(14 TDC72VHL) for TOF400

### Neutron detector

#### **Current status:**

- > 9 TQDC16VS readout modules

- 1G ethernet readout via optical cable

- > TTVXS time sync and trigger via backplane

### BH DAQ

#### **Current status:**

- ➤ 4 TQDC16VS readout modules

- > 1G ethernet readout via UTP cable

### **Future plans:**

> 1G ethernet readout via optical cables

### FHCAL and SCW DAQ

### **Current status of FHCAL DAQ:**

- 8 ADC64s2\_v5 readout modules

- WR synchronization

- 1G ethernet readout via UTP cable

### **Future plans:**

IG ethernet readout via optical MTP and breakout cables

### **Current status of SCW DAQ:**

- 3 ADC64s2\_v5 readout modules

- 1G ethernet readout via UTP cable

#### **Future plans:**

1G ethernet readout via optical cables

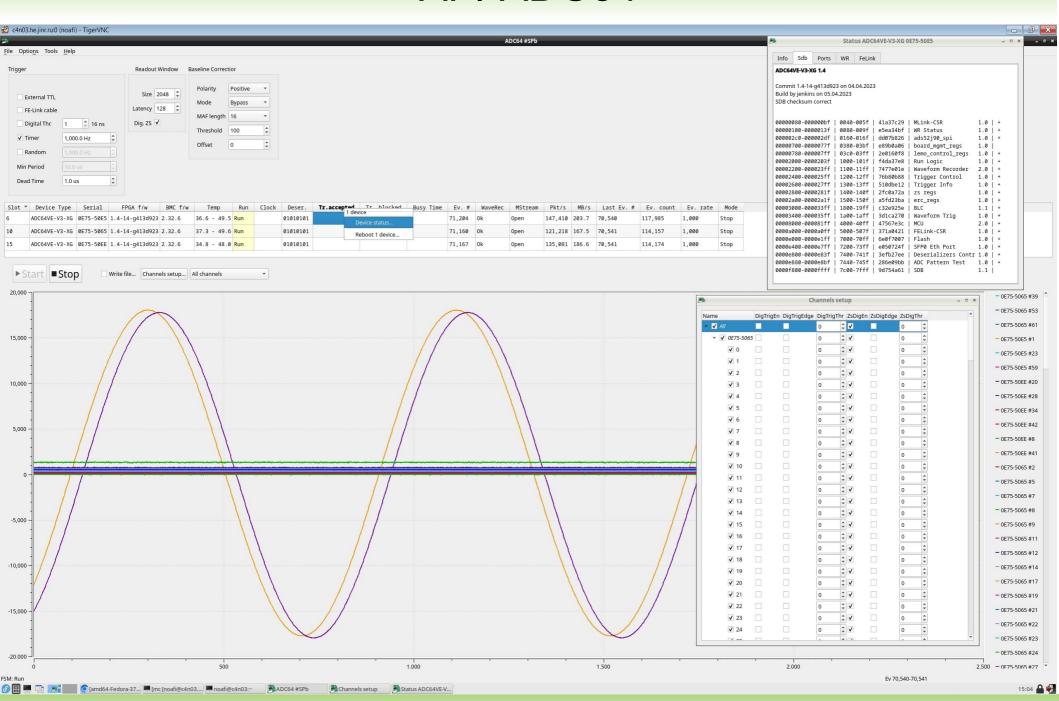

### CSC DAQ

#### **CSC Current status:**

- 8 ADC64VE\_v1 readout modules

- 4 U40VE module as sequencers

- 10G optical link to each ADC board

#### CSCB Current status:

- 4 ADC64VE\_v1 readout modules

- 2 U40VE module as sequencers

- 10G optical link to each ADC board

### **Future plans:**

- Replace second DCH with new CSC

- > Firmware update

- Software update

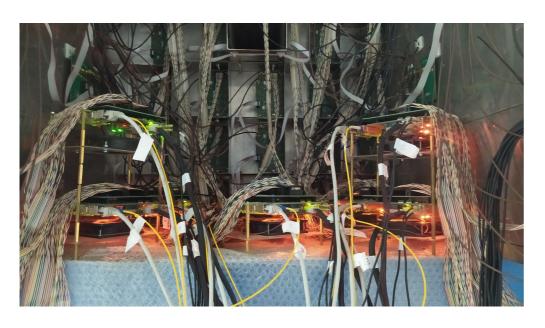

### **GEM DAQ**

#### **Current status:**

- 44 ADC64VE\_v1 readout modules

- ➤ 1 U40VE module as common sequencer for all GEMS

- > 10G optical link to each ADC board

### **Future plans:**

- Firmware update

- Software update

### FSD & BT DAQ

#### **FSD Current status:**

- ➤ 9 ADC64VE\_v1 readout modules

- ➢ 9 U40VE module as sequencers

- 10G optical link to each ADC board

### **Future plans:**

- Firmware update

- Software update

#### **BT Current status:**

- ➤ 1 ADC64VE\_v1 board

- 2 U40VE module as sequencers

- > 10G optical link to each ADC board

### **Future plans:**

- Firmware update

- Software update

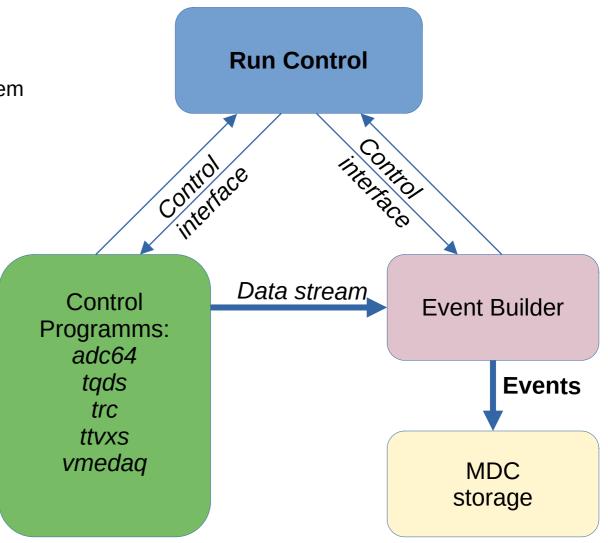

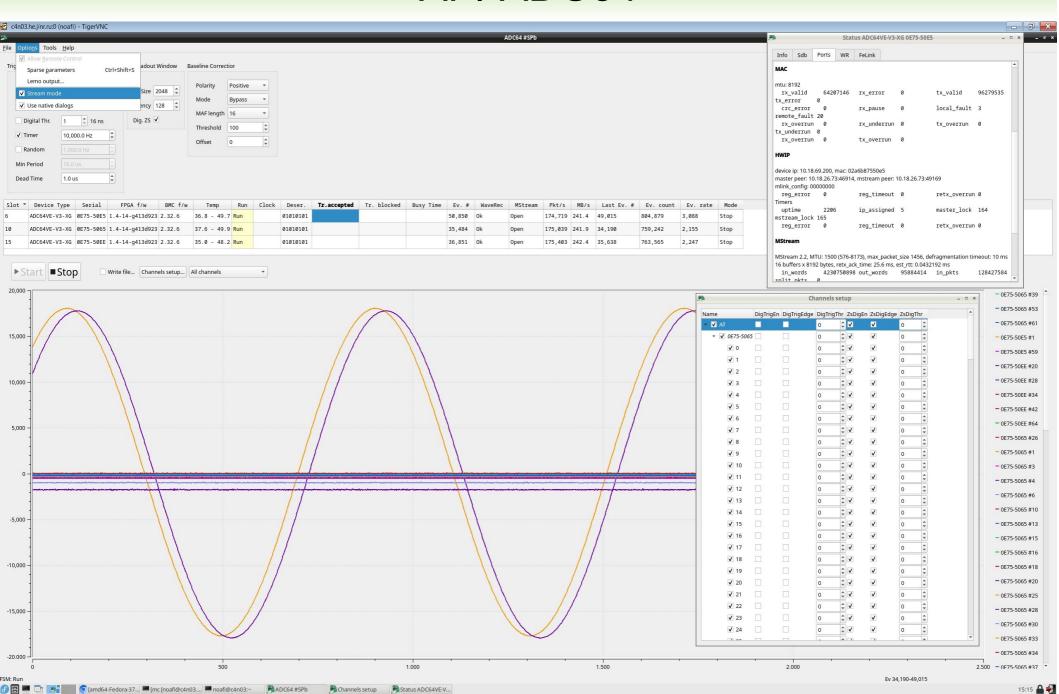

### Software

#### **Current status:**

- Global software rework for modular system

- Developed TRC software

- TDC & TQDC software rework

- Event Builder significant improve (file split, flex parameters etc..)

#### **Next RUN:**

- Reworked ADC64 programm

- Reworked Run Control programm

### AFI-TQDC2

🕜 🗒 💻 📑 🔼 EventBuilder #sav... ☐[AFI Viewer]

### AFI-ADC64

### AFI-ADC64

## Thank you!