# АППАРАТНАЯ РЕАЛИЗАЦИЯ И ТЕСТИРОВАНИЕ 4-Х КАНАЛЬНОЙ БЫСТРОЙ ЭЛЕКТРОНИКИ ДЛЯ ДЕТЕКТОРА НА МКП

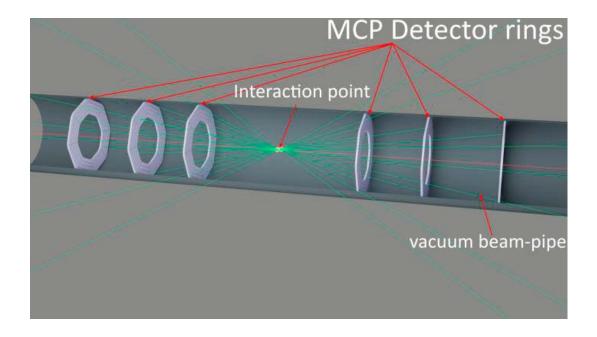

Рис.1 Конфигурация системы, состоящей из шести детекторов на микроканальных пластинах с внутренними кольцами из МКП детекторов

# Два блока детекторов по 32 сегмента — Ионопровод — Собственный — Вакуум Взаимодействия Секторный блок (МКП)

Рис.2. Схема конфигурации детектора № 2. Большие кольца детектора (не в масштабе).

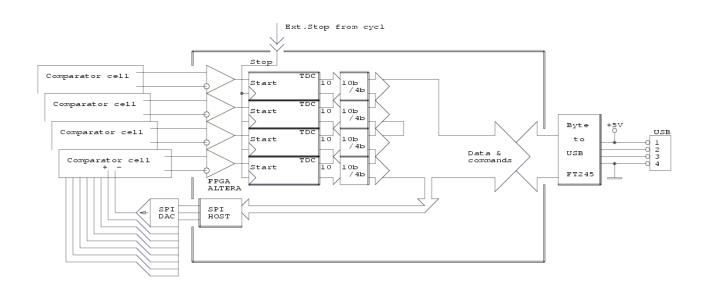

# 2 Система быстрого считывания

Рис.3. Блок-схема четырех каналов регистрации

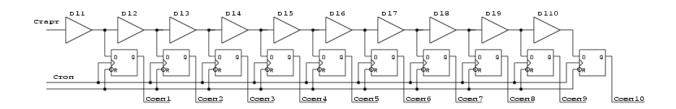

Рис.4. Блок – схема одного из каналов преобразователя время-код (ВЦП)

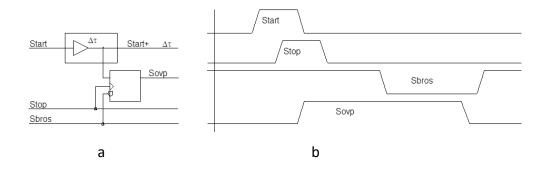

Рис.5. Схема одной ячейки (a) и временная диаграмма (b).

.

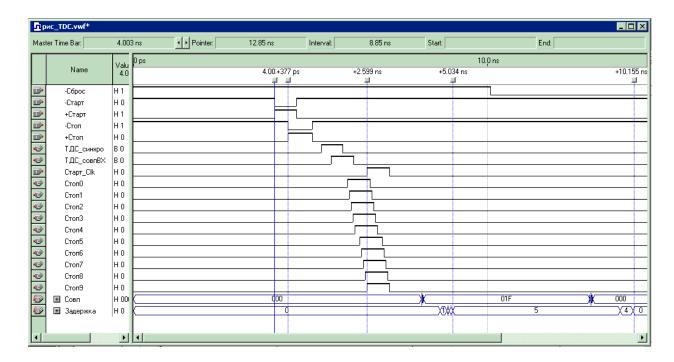

Рис. 6.В диаграмма, полученная в результате моделирования в среде Quartus отработки системой пары импульсов Старт-Стоп со сдвигом 380 пс

### Из рис.6 видно:

- Время работы преобразователя из термометрического кода в двоичный в FPGA для одного канала не превосходит 6 нс, задержка сброса составляет 3 нс.

- для 32 канальной системы регистрации координаты и времени по сигналам с детекторов на МКП, построенной на основе разработанной схемы, с учетом всех задержек полное время обработки не превысит 20 нс.

Рис.7. Модуль 4-х канальной электроники

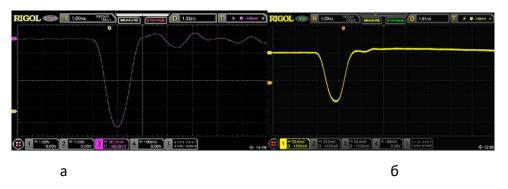

Рис.8. Осциллограммы сигналов от детектора на МКП (a), 20мВ/дел и генератора наносекундных импульсов (б), 50мВ/дел.

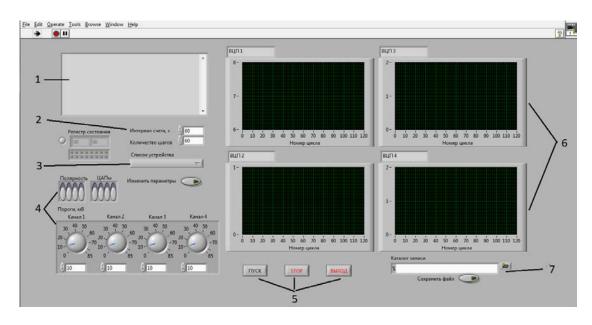

Рис.9. Лицевая панель программы:

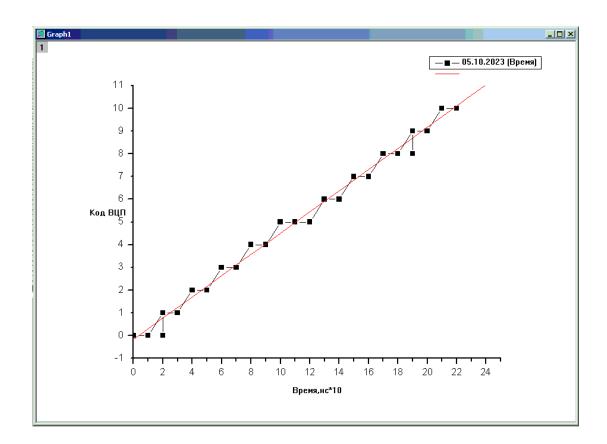

Рис.10. Зависимость кода ВЦП одного из каналов прототипа от вводимой задержки.

Из графика видно, что максимальное отклонение от линейной зависимости составляет  $\pm$  100 пс.

## Выводы

- **1.** Проведенное моделирование работоспособности системы быстрого считывания для монитора столкновений пучков с использованием САПР Quartus показало возможность определения времени регистрации частиц детектором с точностью не хуже  $\pm$  100 пс.

- 2. Разработан и создан прототип многоканального модуля быстрой электроники временной привязки к сигналам с МКП детекторов с использованием дискретных компараторов и многоканального преобразователя время-код на основе FPGA EPM240.

- 3. Написана программа, обеспечивающая возможность работы с модулем.

- **4.** Полученные с использованием генератора данные подтверждают результаты моделирования. Временная разрешающая способность разработанной системы равна  $\pm$  100 пс.

- **5.** Электронная схема, собранная на FPGA EPM240, способна оцифровывать и выдавать сумму зарегистрированных на 32 падах числа частиц (множественность) за время менее 20 нс.