# Time of Flight Detector Status Report

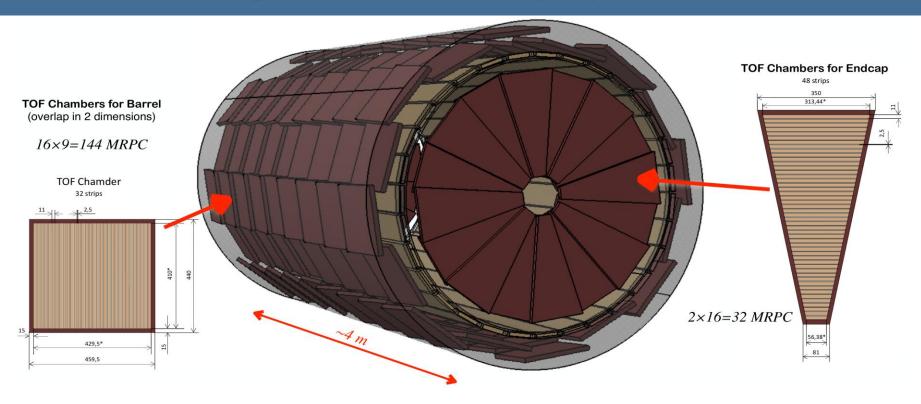

### Time of Flight (TOF) detector proposal

- $\pi/K/p$  discrimination for momenta  $\lesssim 2$  GeV

- Determination of t0

- Time resolution requirement <60 ps.</li>

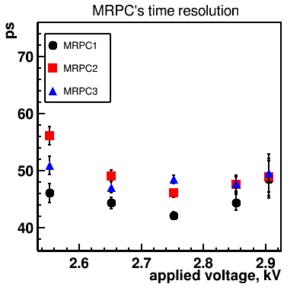

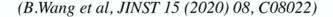

- Sealed (MRPC) are the base option. B.Wang et al, JINST 15 (2020) 08, C08022

- Number of readout for Barrel is 144x2x32=9216 channels.

- Number of readout for Endcap is 32x2x48=3072 channels.

- Total amount is 12288 channels

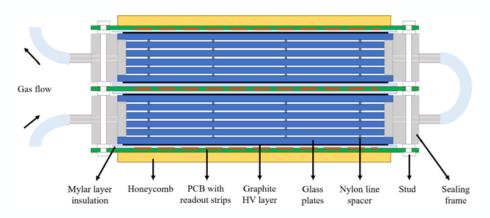

### Sealed MRPC for SPD TOF

(B.Wang et al, JINST 15 (2020) 08, C08022)

Sealed MRPC proposed for CBM-TOF

Sealed MRPC proposed for SPD-TOF

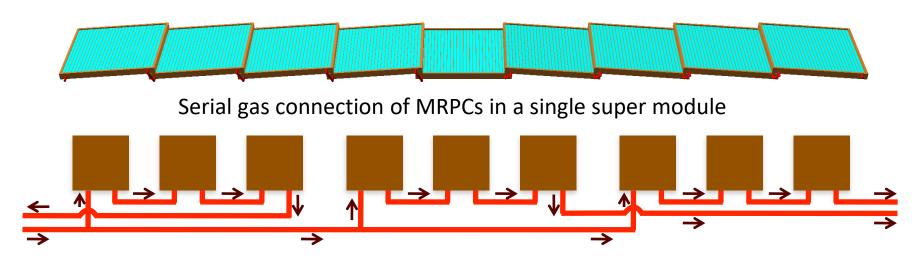

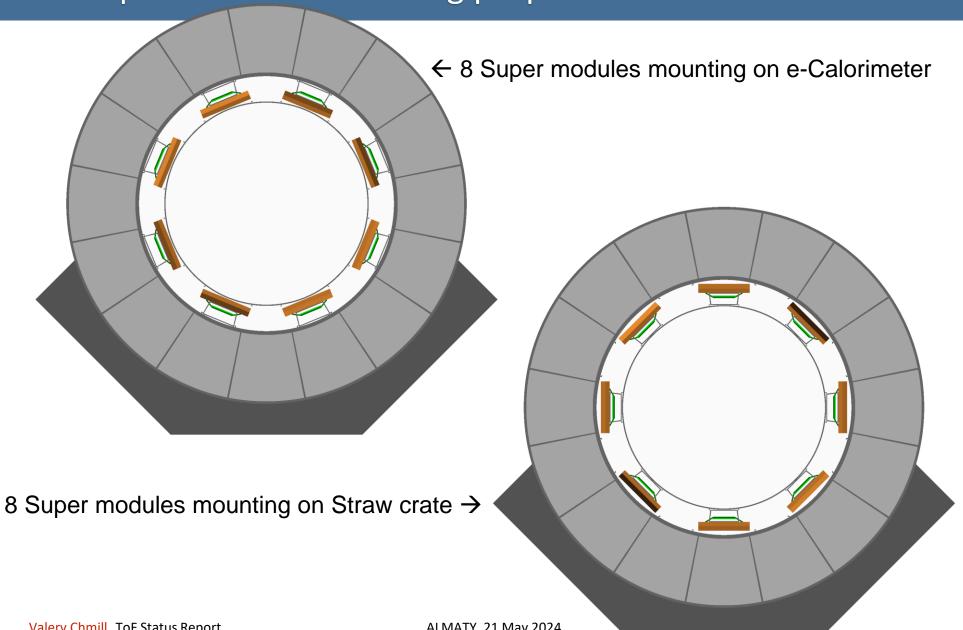

# Super modules mounting proposal

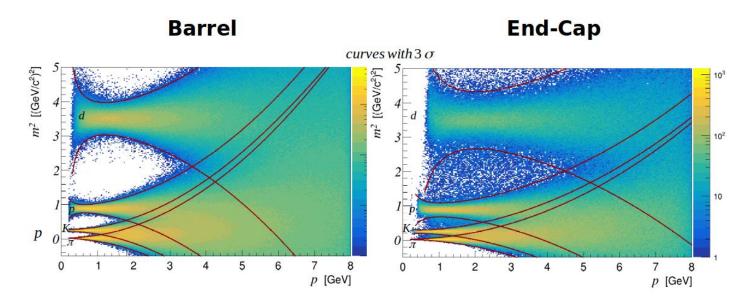

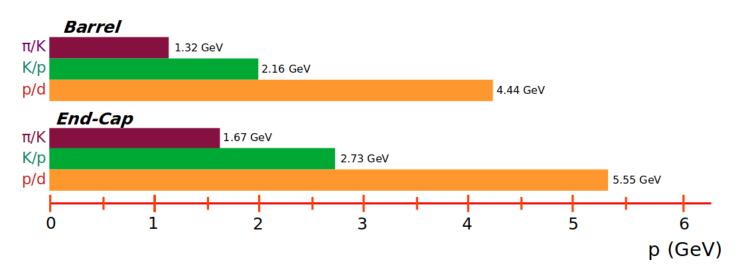

### Particles ID for m<sup>2</sup> vs. p

- π/K/p/d discrimination for momenta <2 GeV</li>

- Determination of t0

- Time resolution requirement <60 ps.</li>

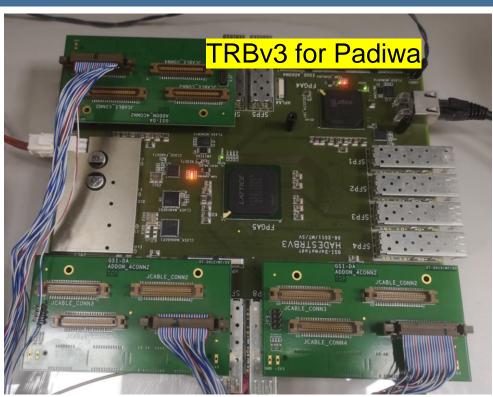

### DAQ (TRBv3) preparation and FEE news

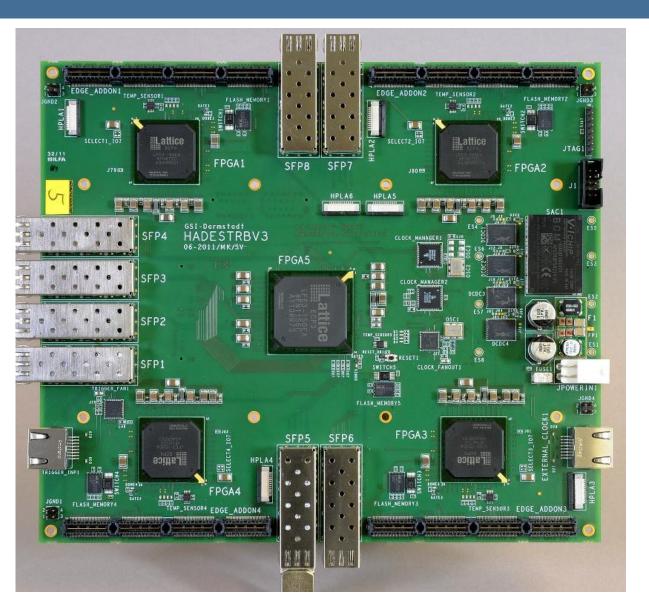

### TRBv3

## TDC-Readout-Board, Triggered/Triggerless-Readout-Board

| ltem                     | Value                                                           |

|--------------------------|-----------------------------------------------------------------|

| Supply Voltage           | 48 V (40-50V), galvanically isolated on board                   |

| Power Supply Current     | 0.5A minimum without AddOns                                     |

| GbE-connectivity         | max. 95 MBytes/s transfer per link                              |

| GbE-slow-control         | up to 400 registers/transfer, speed depends on GbE latency      |

| Connectivity             | Max. 8 SFPs, each 2GBit/s on board. With hub-addon: max. 32 SFP |

|                          | 4 AddONs on top (208 pin), 1 AddOn on bottom                    |

| Max Readout Trigger Rate | about 300 KHz (depending on configuration and network size)     |

| Max Hit Rate             | 50 MHz (burst of 63 hits)                                       |

| TDC Channels             | 260 (Single edge detection)                                     |

| Time Precision           | <20 ps                                                          |

| Minimum pulse width      | <500 ps                                                         |

### TRBv3 FPGA-TDC Based Platforms 128ch in TDC mode

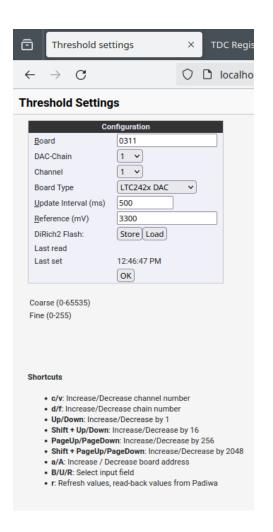

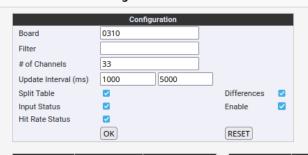

### **WEB GUI**

**TDC Registers**

Threshold settings

| Reg  | Channel       | 0310            |

|------|---------------|-----------------|

|      |               | 3 2 1 0         |

|      | Channel group | on on on on     |

|      |               | off off off off |

| c000 | 0             | 31675           |

| c001 | 1             | _ o             |

| c002 | 2             | □ <b>0</b>      |

| c003 | 3             | 0               |

| c004 | 4             | □ <b>0</b>      |

| c005 | 5             | _ o             |

| c006 | 6             | 0               |

| c007 | 7             | □ 0             |

| c008 | 8             | □ <b>0</b>      |

| c009 | 9             | _ o             |

| c00a | 10            | □ 0             |

| c00b | 11            | _ o             |

| c00c | 12            | □ 0             |

| c00d | 13            | □ 0             |

| c00e | 14            | □ <b>0</b>      |

| c00f | 15            | 31672           |

| c010 | 16            | 31672           |

| c011 | 17            | □ 0             |

| c012 | 18            | 0               |

| c013 | 19            | □ 0             |

| c014 | 20            | □ 0             |

| c015 | 21            | □ 0             |

| c016 | 22            | □ <b>0</b>      |

| c017 | 23            | □ 0             |

| c018 | 24            | □ 0             |

| c019 | 25            | □ 0             |

| c01a | 26            | □ 0             |

| c01b | 27            | _ o             |

| c01c | 28            | □ <b>0</b>      |

| c01d | 29            | □ 0             |

| c01e | 30            | □ 0             |

| c01f | 31            | 31677           |

| c020 | 32            | 31677           |

| Reg  | Content                              | 0310                            |

|------|--------------------------------------|---------------------------------|

| c100 | tdc version<br>channels<br>ref input | 2.1.5<br>32<br>polarity correct |

| c104 | valid trg                            | 14844561                        |

| c105 | valid tmg trg                        | 14844561                        |

| c106 | valid notmg                          | 0                               |

| c107 | invalid trg                          | 0                               |

| c108 | multi trg                            | 0                               |

| c109 | spurious trg                         | 0                               |

| c10a | wrong rdo                            | 0                               |

| c10b | spikes                               | 0                               |

| c10c | idle time                            | 7274799                         |

| c10d | wait time                            | 14227882                        |

| c10f | releases                             | 14844561                        |

| c110 | rdo time                             | 412354                          |

| c111 | timeout number                       | 0                               |

| c112 | data finished<br>number              | 14844561                        |

**TDC Registers**

| JINB |

|------|

|      |

| 0310                      | Content                                       | Reg  |

|---------------------------|-----------------------------------------------|------|

| 0 0                       | Logic Anal.<br>Debug Mode<br>Calib. Prescaler | c800 |

| Disabled on off  Ons  Ons | window en.<br>window bef.<br>window aft.      | c801 |

| 0xc000c000                | act chan 1                                    | c802 |

| 0x0                       | act chan 2                                    | c803 |

| 8                         | data limit                                    | c804 |

| 0x0                       | inv chan 1                                    | c805 |

| 0x0                       | inv chan 2                                    | c806 |

× TDC Registers

DC Registers

× TDC Registers

### **ZOO on SUSE Tumbleweed:**

- VHDL is ranging from the system level down to that of logic gates, for design entry, documentation, and verification purposes.

- Perl Practical Extraction and Report Language.

- **XML** ExtensibleMarkupLanguage for storing, transmitting, and reconstructing arbitrary data.

- C++ (ROOT etc.)

× TDC Registers

×

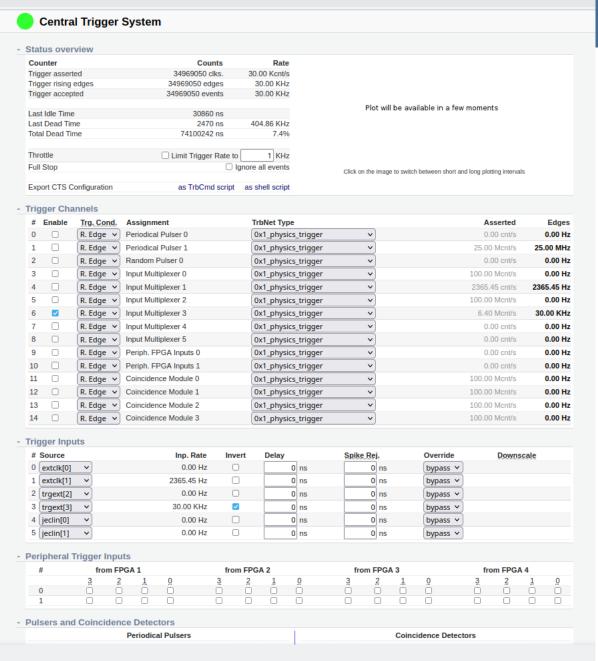

Central Trigger System

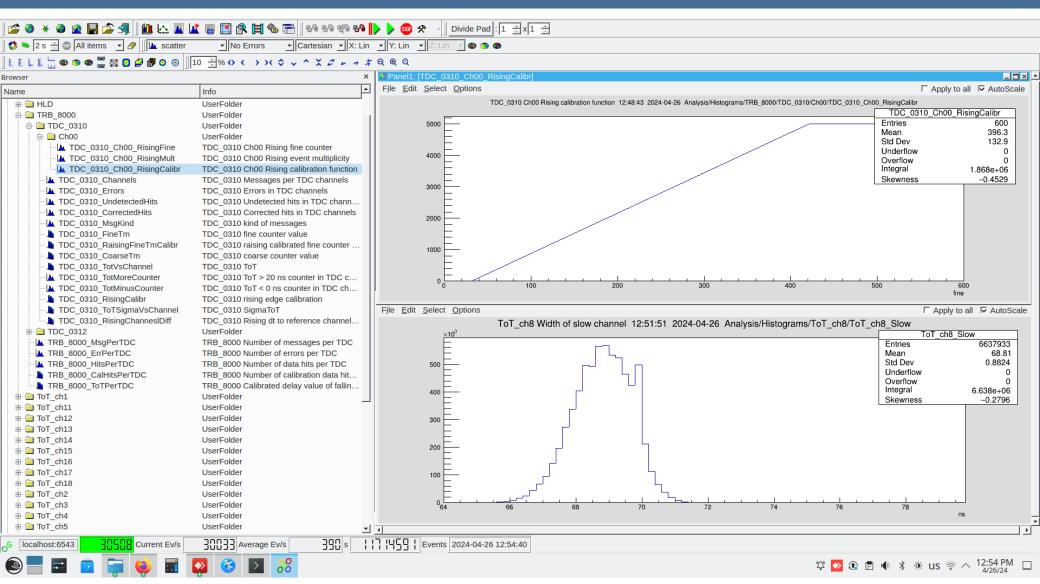

### GO4 for data visualization and analysis

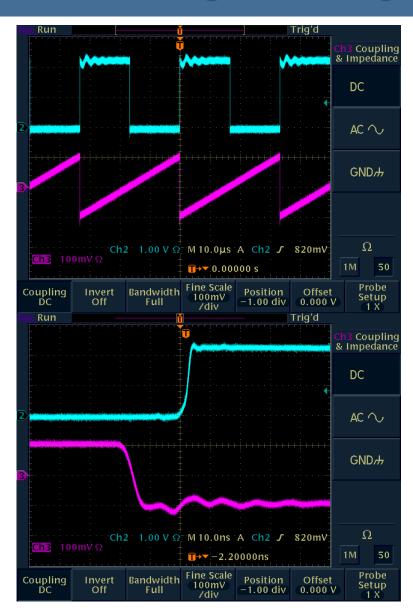

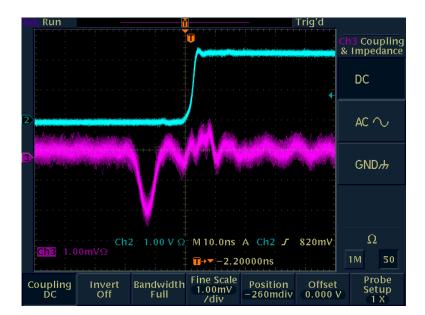

### Test signal forming chains and key parameters

1 pF diff capacitance  $\rightarrow$  200mV = 200 fC

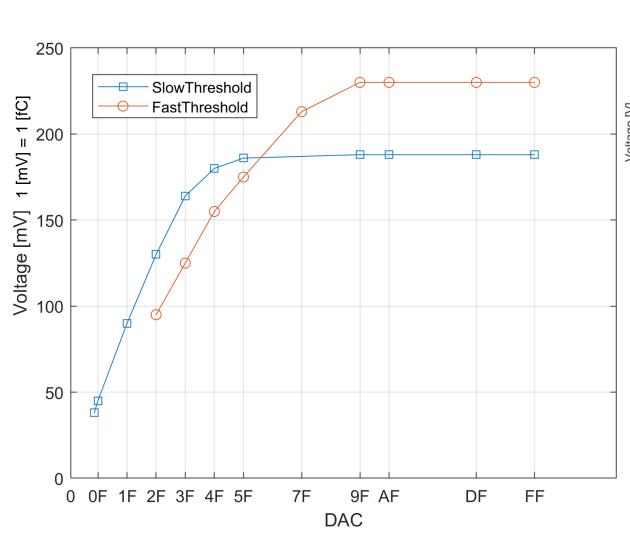

### Threshold for Fast and Slow FEE output

Counts on Fast and after for Slow channels becomes equal to triggers number (Threshold)

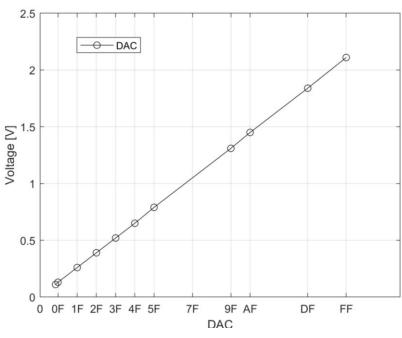

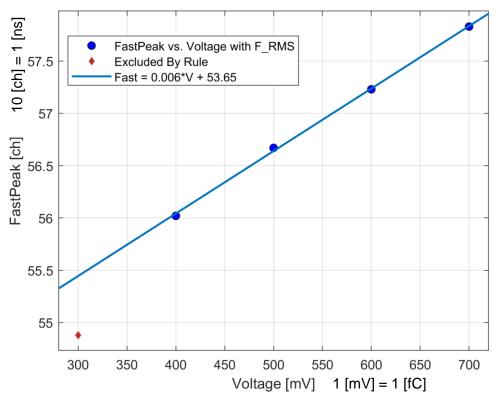

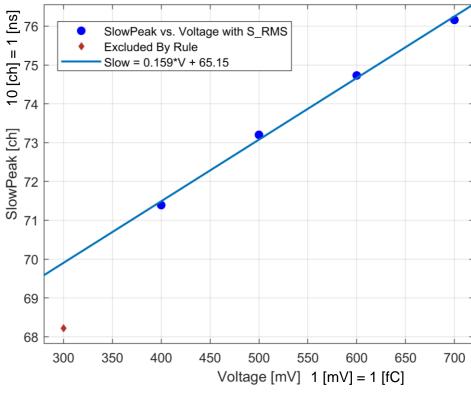

### Linear response to test signal for Fast and Slow output

### Fast peak width 5.5-6ns STD<100ps

#### Slow peak width 7-7.6ns STD<90ps

### Possible FEE and Digitization

#### https://www.caen.it/subfamilies/fers-5200/

- Sensor (SiPM)

- ASIC (WEEROC family, citiroc-1A)

- FPGA

- Data Transmitting

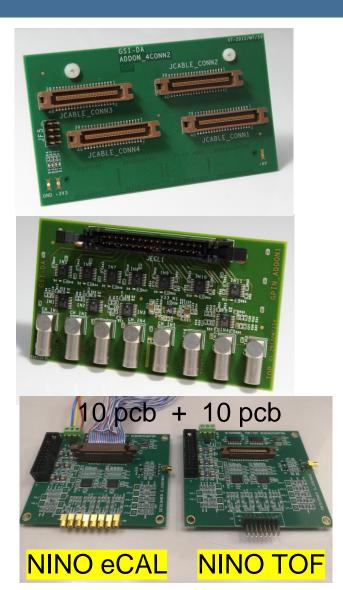

- Sensor (MRPC) + NINO

- ASIC (picoTDC)

- FPGA

- Data Transmitting

#### Front-End Readout System

• FERS A5202

FERS A5203

FERS Concentrator Board DT5215

#### http://trb.gsi.de/

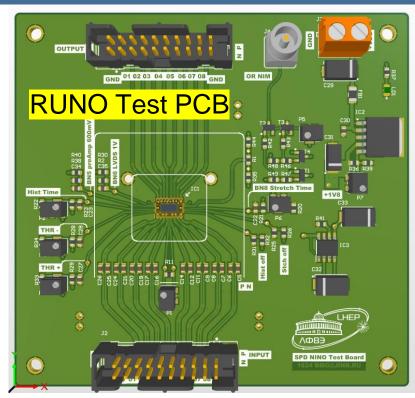

- Sensor (SiPM) +RUNO

- TRBv3 TDC

- ToT method

- Data Transmitting

- Sensor (MRPC) + RUNO

- TRBv3 TDC

- ToT method

- Data Transmitting

TRBv3 contains front-end electronics and a complete set of data acquisition and control software.

### FERS FERS+NINO vs. TRBv3 FPGA-TDC+RUNO

### The only way to do great work is to love what you do. © S.J.

- Artem Semak, Evgeni Ladygin

- Sergei Morozov, Evgeni Usenko

- Artem Ivanov

- Vladimir Ladygin, Aleksey Tishevsky

- Vadim Babkin, Mikhail Buryakov, Sviatoslav Buzin

- Yi Wang at al.

- Michael Traxler & the TEAM

### Thank you for your attention

# Spare slides

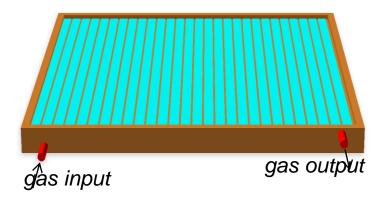

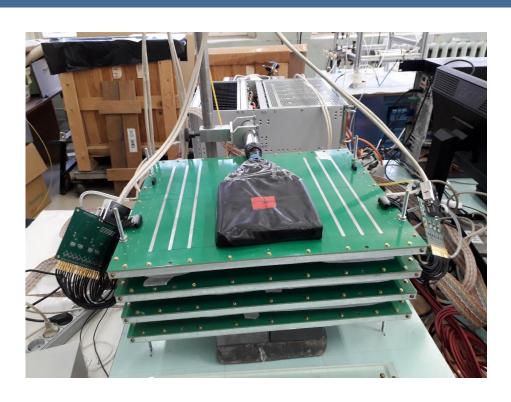

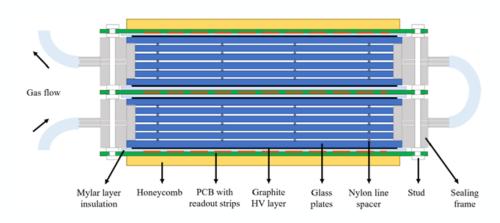

### Protvino MRPC prototype for SPD project at NICA

- To start MRPC and check functionality

- To obtain detection efficiency and time resolution on a new DAQ

- Preparation for using 3 MRPC as a servicing system at TEST AREA (Anton Baldin).

### Sealed (MRPC) are the base option of today

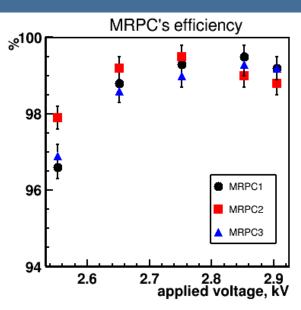

- The prototype was tested in cosmic rays along with 2 MRPC2 counters in the TRBv3 test stand.

- The plateau efficiency is 97%, with a 1.6 cluster size and a 100 ps flight-time resolution.

- The systematic time resolution of the prototype is about 60 ps. if we reasonably expect the same timing precision between two MRPCs.

- The prototype has the same working point at ±5.4 kV with standard gas flow (Freon/iC<sub>4</sub>H<sub>10</sub> = 90/5/5

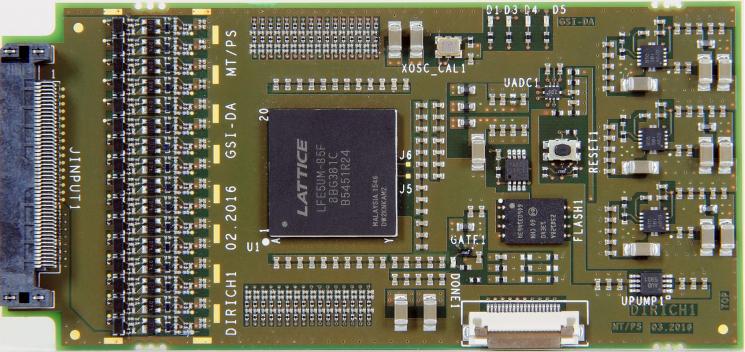

### **DiRICH**

The DiRICH module is a 32-channel transformer, amplifier (factor 30), discriminator (with thresholds settings), **Ops RMS** time precision TDC (currently, can be improved) and finally readout of the data via TRBNet. So, it is an improved version of the combination of a Padiwa + a small part of the

TRB3.