## **Current status of DAQ system**

# Leonid Afanasyev on behalf of DAQ group

## Purchase of equipment

- 1.Computer servers 5 pieces

- 2. White Rabbit Evaluate packages 3 pieces

- 3. Prototype of L2 card

## Stand for development of DAQ and on-line filter

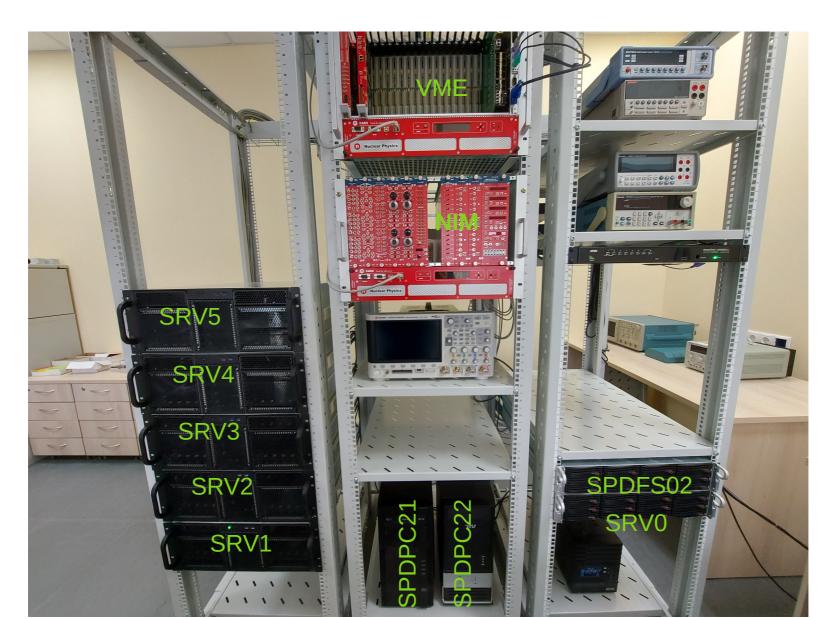

- In September November 2023 we have purchased 5 computer servers.

- During September 2023 April 2024 the special room/lab in LIT was rebuilt and fully equipped. It includes all network environment and the full climate control for personal and computers

Stand for development of DAQ and on-line filter

## Stand for development of DAQ and on-line filter

The network structure have been fully configured. It includes the lab in LNP at distance of about 1 km. A good condition for emulation of our future experimental aria.

## White Rabbit development kits for TSS

During June – November 2023 we purchased 3 White rabbit switch Evaluate packages from China, Sync (Beijing) Technology co., LTD.

White Rabbit switch WRS-18A - 3 pieces

Cute-WR-A7-PKG – WR node 6 pieces

Now we have the tools for development of our synchronization system. The first results will be presented in the next talks.

## Development board for L2 concentrator

From April 2024 we are purchasing the prototype of L2 concentrator card: ZYNQ UltraScale+ FPGA Development Board Z19-P form Alinx.

In case of success we will have the tools for implementation of our L2 concentrator.

The first results of L2 development will be presented in the next talks.

## Front-end electronics for the triggerless DAQ

Front-end electronics of the detectors has to meet the requirements of a free-running DAQ

#### <u>General FEE requirements</u> from the DAQ system:

- Self-triggered (trigger-less) FEE operation

- Digitizing on-board

- Timestamp included in the output format

- Large memory to store the data accumulated in a time slice

- Zero suppression

FPGA or ASIC based digital output to DAQ

For the moment only Range System has the Front-End electronics designed according to these requirements (high level of readiness)

## Front-end electronics for the triggerless DAQ

### PCB of L1 concentrator (prototype)

- Cyclone 10GX (105YF780E6G)

- 8x Links for connect front-end boards (miniSAS\* connectors) 8 diff pairs per connector

- SFP+ 10Gb transceiver for data transmission to L2

- SFP+ 10Gb transceiver for TSS (White Rabbit)

#### Concentrator tasks:

- Collecting data from the front-end boards.

- · Distribution of clock from TSS.

- Distribution of commands from TSS.

- Data integrity and timestamp control.

- Reconfiguring front-end boards (firmware)?

<sup>\*(</sup>additional info on presentation slide 6)

## **Open questions**

- Front Electronics cards exists for RS only. We NEED contribution from all other detector groups.

- Where L1 Concentrator will be installed: inside or outsides the Range system? (e-link <10m)</li>

- Radiation hardness of FPGA, in the case of installation of L1 Concentrator inside the Range system

- Which Time Synchronization: White Rabbit or TCS?

## Continue R&D

## **Progress**

We have the really working collaboration for development of the DAQ hardware:

JINR Dubna,

St. Petersburg Polytechnical University, Tomsk State University.

Agreement with iThemba LABS, National Research Foundation, South Africa (ZA) for development of the software part of DAQ. (report on 23<sup>rd</sup> May at 10:00)

## Thank you for your attentions.