# Status of L1 concentrator

**Aleksandr Boikov**

on behalf of DAQ group

E-mail: Boikov@jinr.ru

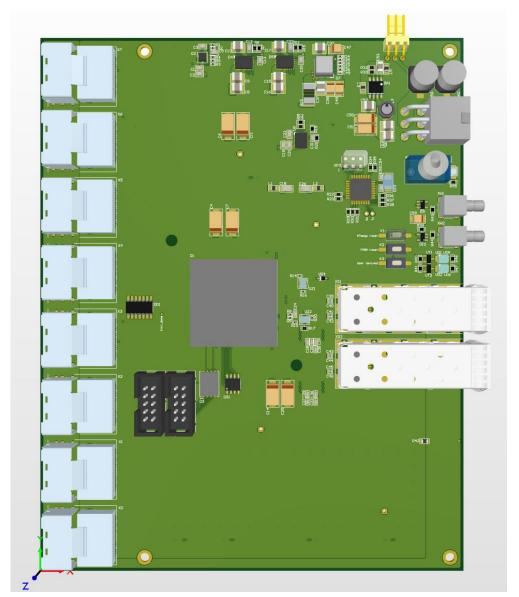

### PCB of L1 concentrator (prototype)

- Cyclone 10GX (105YF780E6G)

- 8x Links for connect front-end boards (miniSAS\* connectors) 8 diff pairs per connector

- SFP+ 10Gb transceiver for data transmission to L2

- SFP+ 10Gb transceiver for TSS (White Rabbit)

#### Concentrator tasks:

- Collecting data from the front-end boards.

- Distribution of clock from TSS.

- Distribution of commands from TSS.

- Data integrity and timestamp control.

- Reconfiguring front-end boards (firmware)?

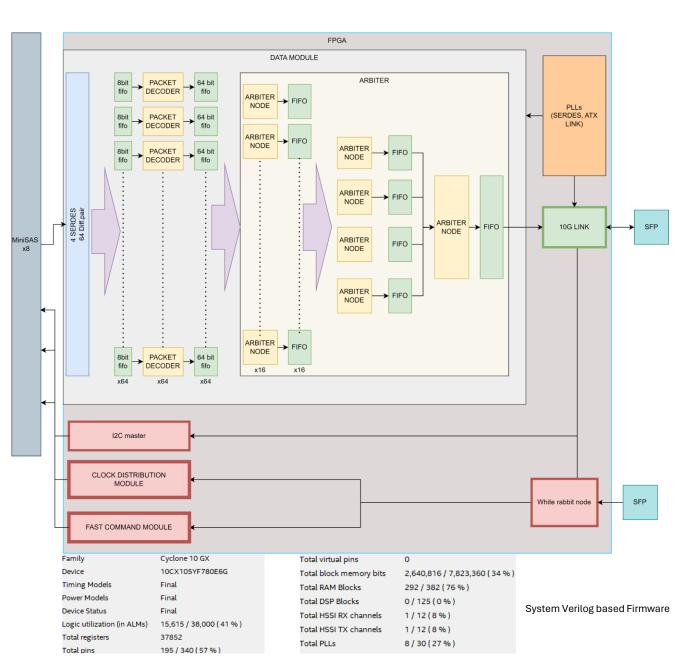

### L1 Firmware (first iteration)

First version of modules

Ready:

- ✓ 10G Link (UPD packet, ARP, PING) Without Soft-Core processor.

- $\checkmark$  Data collect module for custom protocol\*.

- ✓ I2C master for slow control command.

(can be change to another protocol)

Not ready:

X TSS node (SPbPU will provide).

X Clock distribution module.

X Fast command module.

X Another optional modules.

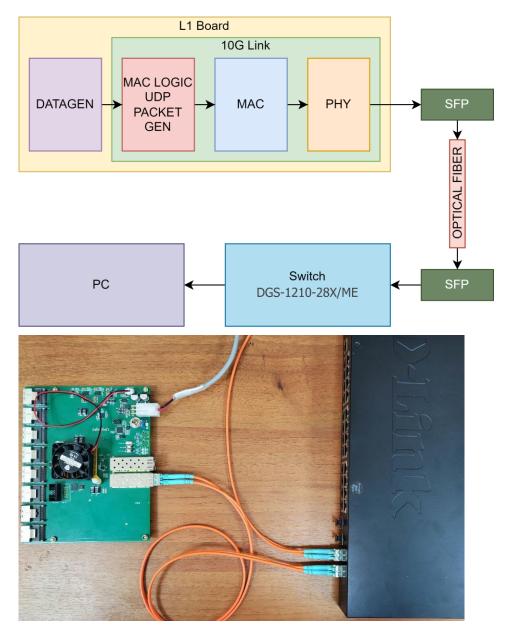

### 10G Link Bandwidth measurement

- SFP: Finisar FTLX8571D3BCV

- SWITCH: D-LINK DGS-1210-28X

- One hour test average bandwidth (speed): 9.928551 Gbit/sec

- UPD packet

- Fixed packet size: 1518 bytes

- Average bandwidth (speed) for payload : 9.876227 Gbit/sec

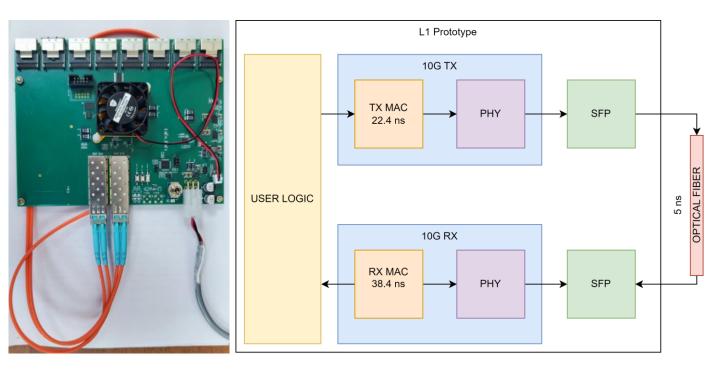

### 10G Link Latency measurement

- Test in loopback mode

- Fiber length: 1m

- SFP: Finisar FTLX8571D3BCV (850 nm)

- Max fiber length: 300m

- Consumed: 1 watt

#### Total delay TX to RX: ≈ 266.8 ns

| • Fiber:                      | ≈5 ns     |

|-------------------------------|-----------|

| TX MAC                        | 22.4 ns   |

| RX MAC                        | 38.4 ns   |

| <ul> <li>PHY + SFP</li> </ul> | ≈2x100 ns |

| Latency v                         | vitl      | hout l    | MA  | AC IP     | *   |     |     |          | 206ns |     |     |     | <b>→</b> |                       |    |     |     |           |

|-----------------------------------|-----------|-----------|-----|-----------|-----|-----|-----|----------|-------|-----|-----|-----|----------|-----------------------|----|-----|-----|-----------|

| 6:14 (0:0:2.2 elapsed)            | +         |           | •   |           | 127 |     |     |          |       |     |     |     | +12      | 9                     |    |     |     |           |

| Name                              | 127       | Value     | 128 | 96 112    | 128 | 144 | 160 | 176      | 192   | 208 | 224 | 240 | 256      | 272                   |    | 288 | 304 | 320       |

| <sup>.</sup> xgmii_tx_control[30] |           | 1h        |     | Fh        |     | Oh  |     |          |       |     |     |     | Fh       |                       |    |     |     |           |

| <sup>.</sup>  xgmii_tx_data[310]  | $\square$ | 555555FBh |     | 07070707h |     |     |     |          |       |     |     | 0   | 707070   | 07h                   |    |     |     |           |

|                                   |           | Fh        |     |           |     |     |     | Fh       |       |     |     |     |          | <u>)</u> 0            | h  | X   |     | Fh        |

| <sup></sup>                       |           | 07070707h |     |           |     |     |     | 7070707h |       |     |     |     | 18       | CALACTERIA CONTRACTOR |    |     |     | 07070707ł |

| ac_phy phy_10g csr_clk            |           | 1         |     | uuuu      | ЛL  | nnn | பா  | vvv      | uu    | JUL | JUU | uu  | תת       | un                    | лл | ΓLU | лл  | UUU       |

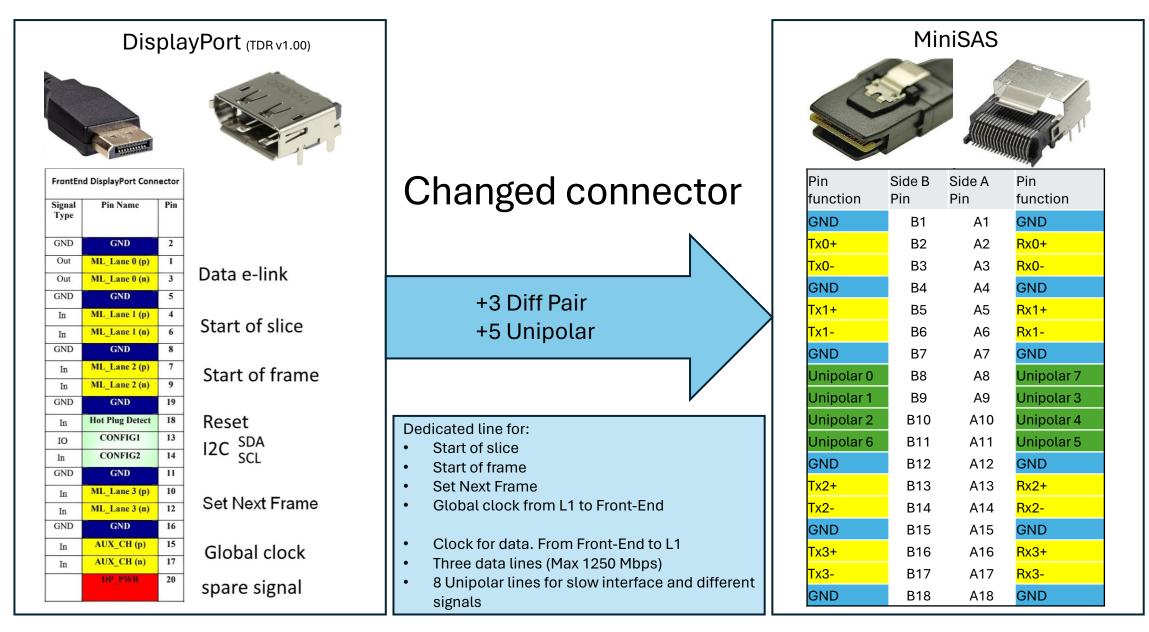

### E-Link port

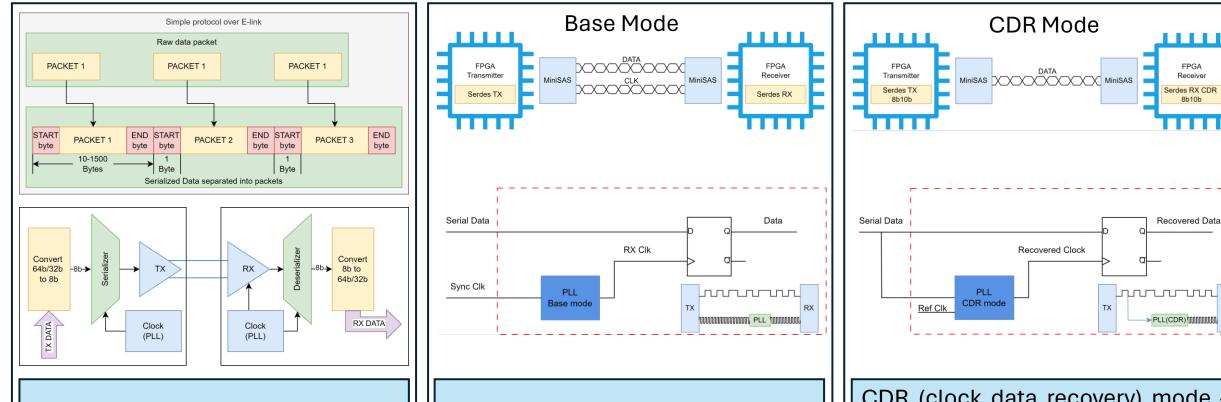

### E-Link data serialization (options)

A simple transfer protocol was prepared for first test. In data append start and end bytes for data packet separation.

Data serialize and send over MiniSAS cable.

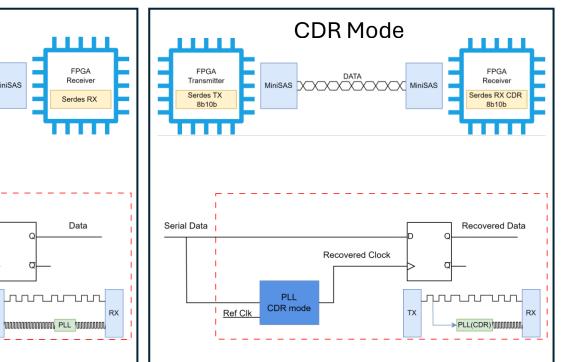

Base serial mode – using dedicated lines for data and synchronization clock for transfer. Stable for high bandwidth and long line due to dedicated clock line.

CDR (clock data recovery) mode using one line for transfer. Clock is recovered from data\*. Phase of recovered clock is synchronizing with reference clock.

Increased jitter requirement for the source.

\*The Front-end should implement serialize procedure with 8b/10b encoding

FPGA

Receiver

8b10b

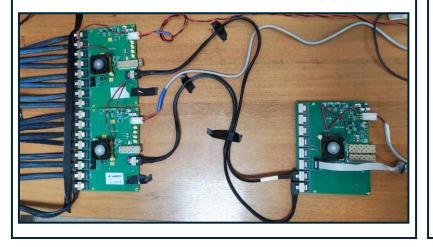

### E-Link test

- Two data generator boards 1.

- 2. L1 concentrator prototype

- Two MiniSAS cable (1m) 3.

- 24 hour test for each modes 4.

#### Monitoring via JTAG

Link bandwidth per line: 150 Mbps – OK 500 Mbps – OK 750 Mbps – OK 1000 Mbps – OK 1250 Mbps – OK

**Base Mode**

RX Clk

PLL

Base mode

FPGA

Receiver

Serdes RX

Data

www.www.PLL www.w

MiniSAS

....

FPGA

Transmitter

Serdes TX

Serial Data

Sync Clk

Link bandwidth per line\*: 150 Mbps – OK 500 Mbps – OK 600 Mbps – OK 750 Mbps – ERRORS 1000 Mbps – ERRORS

\*may reach 1200 Mbps after modifications

## Thanks for your attention