## L2 concentrator firmware

Vladislav Borshch On behalf of TSU SPD electronics group

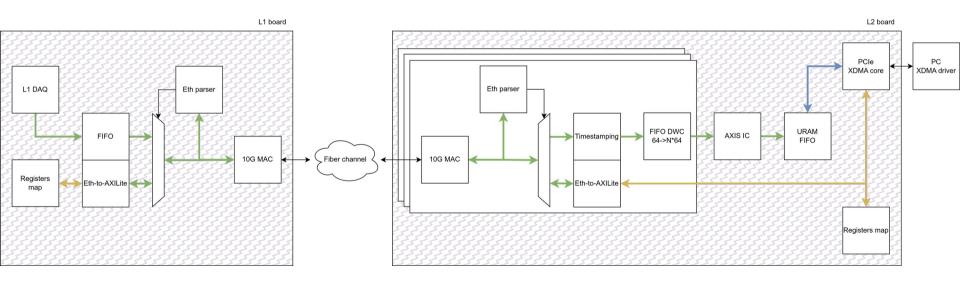

## L2 FPGA architecture

AXI4MM

AXI4Lite

AXI4Stream

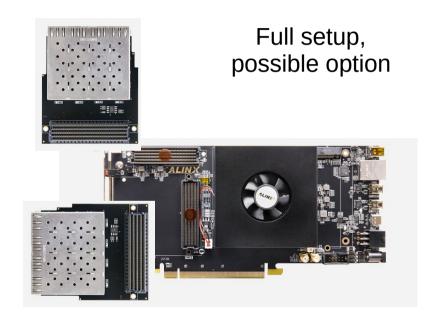

## **Platform**

#### Limited setup, Xilinx's analog

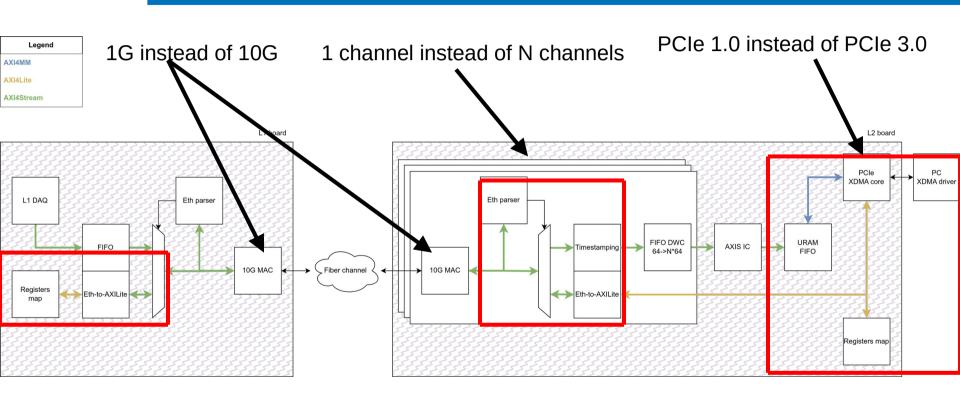

# L2 FPGA progress. Limited setup

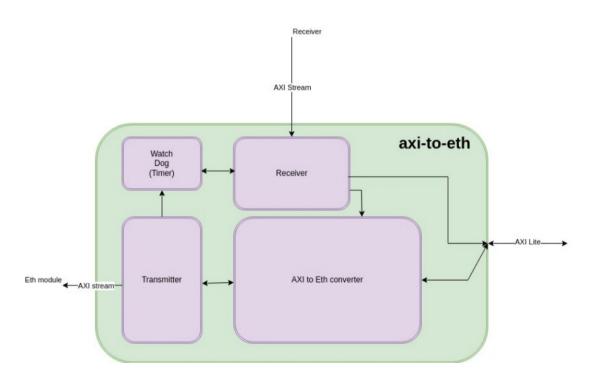

## **AXI-Ethernet transport**

Receiving logic: prepared ethernet frame gets converted to AXI Lite.

Sending logic: AXI Lite command is converted to the Ethernet frame and then gets sent by the Ethernet interface

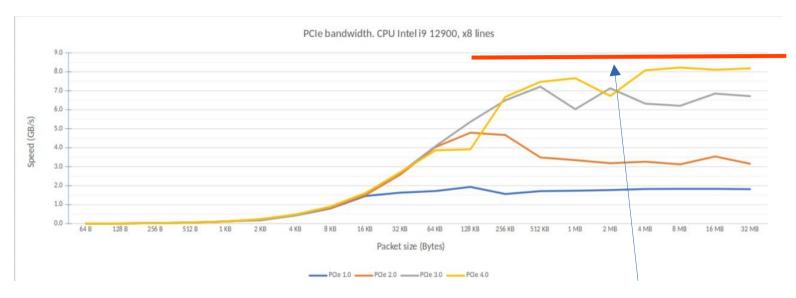

#### PCI C2H bandwidth

#### Preliminarily result with various PCIe configuration

Kind of "bottleneck" because of CPU (100% load at this point). Might be investigated and optimized in case of needs