# Status of TPC LV, TPC GATE systems and FE cards tests

Electronic methods and mens of experiment laboratory:

Tchekhovski V.A. head <u>E-mail</u>

Litomin A.V.

Galkin Y.D.

Kunts A.V.

+outsourse

Buglak S.

Korotkiy I.

Speaker: Yaroslav Galkin

# TPC GATE systems

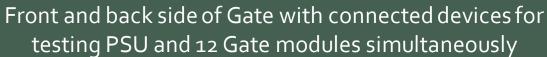

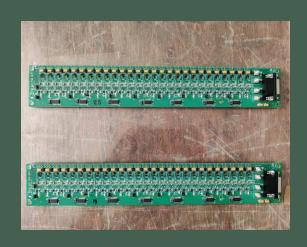

Front and back side of 1 Gate crate, in top-12 Gate modules, in bottom PSU

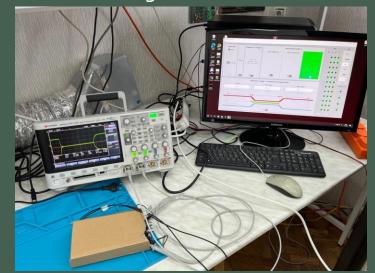

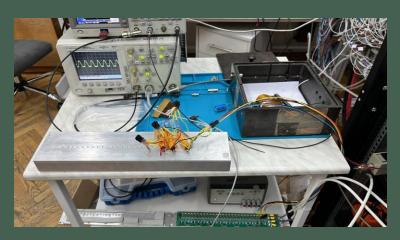

Test bench for 1 module of 1 gate crate

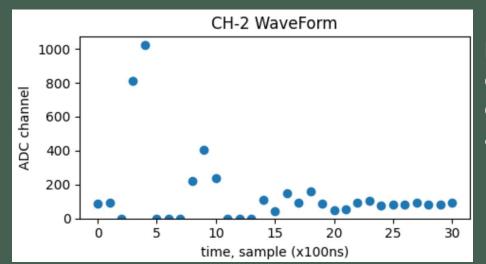

Example of open/close transiti on process, is about 2 us

### TPC LV

Power cable for FEC

2 LVN9 with old r-angle DSUB

Test bench for LVN9, RL ~ 4 FEC

DSUB 26 pin with steel case

Molex Nano-Fit 12 and 16-pin

us/products/partdetail/2014441112

### New output capacitors:

- Ceramic CL31A107MPKNNWE ESR ~0.01 Ом (MIN на 5-10 MHz)

- Polimer T520C107M006AME025 ESR 0.025 OM ESR @100 kHz/ +20 °C Soldered off:

- Tantalum TAJC476Ko2oRNJ ESR 0.500 Ом ESR @ 100 kHz/+20 °C

Test bench ROC LVN9 output voltages increased to 1.8, 3.1, 3.8 V

# FEC testing

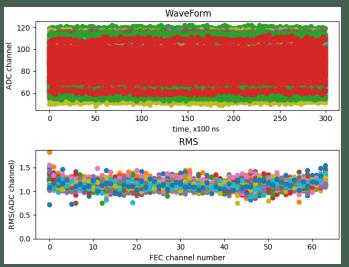

Example of 10 events data for 31 card from ROC

PCB with Ccal=2pF

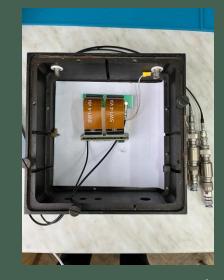

Cast iron case with FEC connected by flexible PCB to PCB with Ccal

WaveForm of CH-48 event-0 from file runs/454/0pF/raw/54-454.txt

800 - Amplitude=727.3

Baseline=100.7

Min=99.3

500 - Min=99.3

100 - Min=99.3

Example of SAMPA curve fitting

FEC test parameters: AFG3152C pulse 400mV at.-20dB ~ 80fC, Tran=3ns

# Thank you for attention