FLNP JINR – CSNS Workshop on the neutron scattering technology and multi-disciplinary research International Conference Centre, Dubna

# Working with the CAEN DT5560SE digitizer

a project for processing signals from a helium-3 filled positionsensitive detector.

Speaker: electronics engineer

Department of spectrometer complex IBR-2 FLNP JINR

Anastasiya Kazliakouskaya

nasta94@jinr.ru

FLNP JINR – CSNS May 13-15, 2024

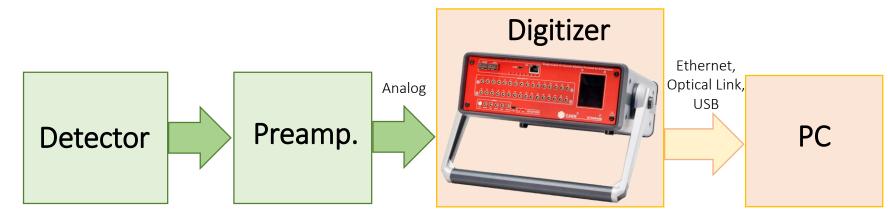

## Digitizer in the data acquisition system

*Digitizer* – is an electronic device that continuously acquires analog pulses, passing through an analog input stage of signal conditioning, an **analog-to-digital conversion** by fast ADCs, and **storage** of the digitized samples as event data into digital memories, where they can be **read out** by a host computer through fast communication interfaces (USB, VMEbus, Optical Link, Ethernet).

Figure 1. Structure of a digitizer-based data acquisition system

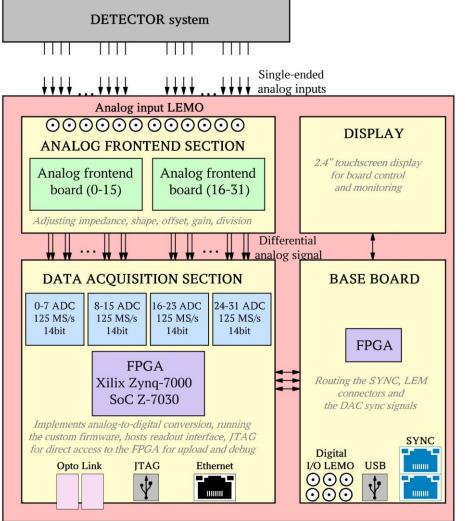

#### *Digitizer DT5560SE*:

- 32 channel, **14-bit @125 MS/s** Digitizer,

- Programmable analog frontend,

- Xilinx Zynq-7000 SoC with **open FPGA**,

- Supported software tool by SCI-Compiler,

- Board-to-board synchronization, etc.

Figure 2. Front panel view.

Figure 3. Block diagram of DT5560SE digitizer device

| /// <b>DT5560SE</b>                                                                                                  | =                                                                                                                                                 | DEVICE PID: XXXXX                                                |                                       |             |               |                            |          |                                      |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------|-------------|---------------|----------------------------|----------|--------------------------------------|

| <ul> <li>☆ Device Status</li> <li>☆ Analog Settings</li> <li>• I/O Settings</li> <li>☆ BEthernet Settings</li> </ul> | Device Status DEVICE MODEL: DT55605E-A  Device Info IP: XXX.XXX.XXXX USB: XXX.XX PID: XXXXX Pramework 2024.03 Release:                            | K.XXX.XXX<br>.06 ▲ Upgrade Device                                | I/O Settings<br>Clock Input<br>Source | nternal 🗸   |               |                            |          |                                      |

|                                                                                                                      | Base Board Info<br>Firmware 21041200 Temperature: 30.6 °C<br>Release:                                                                             | Analog Boards Info Temperature 1: 42.7 °C Temperature 2: 44.4 °C | DAQ Sync In                           | 0           | Sync Out      | 0                          | Lemo Out | 0                                    |

|                                                                                                                      | DAQ<br>Info                                                                                                                                       |                                                                  |                                       | .emo ln 1 🗸 |               | Sync In 0 V<br>Sync In 1 V | 1        | DAQ Sync Out 0 V<br>DAQ Sync Out 1 V |

|                                                                                                                      | Firmware Name:     NEW_QMP4     Change DAQ       Firmware Release:     20240408     Firmware       Temperature:     48.7 °C     Sownload Register |                                                                  | 2 L                                   | .emo ln 2 🗸 |               | Sync In 2 👻                | 2        | DAQ Sync Out 2 💙                     |

|                                                                                                                      | Version 2023.12.06. All rights reserved.                                                                                                          | CAEN NUCLEAR<br>Faith for Descent NU Instruments                 |                                       | <b>C:</b> _ |               |                            | _        |                                      |

| Figu                                                                                                                 | Figure 4. Embedded Web interface home page.                                                                                                       |                                                                  |                                       | Fig         | ure 6. I/O Se | ettings page               | e.       |                                      |

Figure 4. Embedded Web interface home page.

| aper |                |                    |               |                          |                         |           |

|------|----------------|--------------------|---------------|--------------------------|-------------------------|-----------|

|      |                |                    |               |                          |                         |           |

| 2    | DC             | *                  |               |                          |                         |           |

|      |                |                    |               |                          |                         |           |

|      |                |                    |               |                          |                         |           |

|      |                |                    |               |                          |                         |           |

| 1    |                |                    |               |                          |                         |           |

| 1    | Channel        | 50 Ohm Termination | Division by 5 | Offset Even (mV)         | Offset Odd (mV)         | Gain      |

| 1    | Channel<br>0-1 | 50 Ohm Termination | Division by 5 | Offset Even (mV)<br>0.00 | Offset Odd (mV)<br>0.00 | Gain<br>1 |

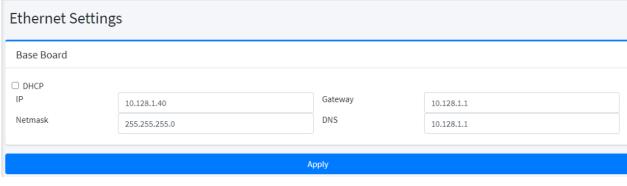

#### Figure 7. Ethernet Settings page.

SCI-COMPILE

**Open FPGA**

FLNP JINR – CSNS May 13-15, 2024

## Graphical Programming Language for CAEN Open FPGA boards

- Block Building Interface

- Automatic Firmware Code Simulation

- Debug with Resource Explorer

*Sci-Compiler* uses a set of high level functionalities (IP blocks) to mask the real firmware coding, which improves and speeds-up the R&D phase. Placing and interconnecting the available blocks on a diagram, it is able to automatically generate a VHDL code that implements the required function and deploy it to the FPGA.

| S Nucle | ear Instrum             | ents SciCon     | piler (2024        | 4.1.6.1) -           | NEW_QM                | P3                    |                 |     |                   |

|---------|-------------------------|-----------------|--------------------|----------------------|-----------------------|-----------------------|-----------------|-----|-------------------|

| -       | Home                    | Tools Box       | View Sin           | nulation             | Compile               | Hardware              |                 |     |                   |

|         | 1010<br>0111            |                 |                    | Ţ,                   |                       | 0                     | =               | :   |                   |

| Misc    | Bitwise<br>Operations * | Sub-design      | State<br>Machine * | Boolean<br>Logic *   | Sequential<br>Logic * | Timer<br>Counters *   | Comparator<br>* | Mux | Delay<br>Memory * |

|         | I/O, Wire               | es, Subdesign   |                    |                      |                       | Log                   | gic             |     |                   |

|         |                         |                 |                    | 2                    | 7                     |                       | _               |     |                   |

|         |                         | G               | $\mathbf{O}$       |                      | 22                    | 01011                 |                 |     |                   |

|         |                         | Math<br>Filters |                    | Signal<br>Analysis * | Trigger               | Signal<br>Generator + |                 |     |                   |

|         |                         |                 | Signal F           | Processing           |                       | Testing               |                 |     |                   |

Figure 8. Tools Box with 100+ virtual blocks that works exactly as real laboratory instrumentation

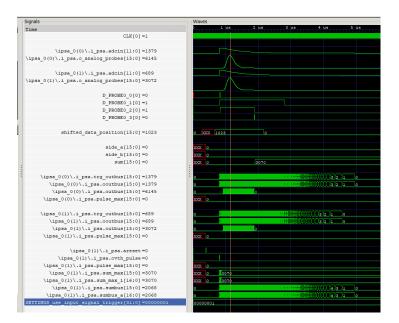

## Automatic Firmware Code Simulation

Sci-Compiler allows to simulate the firmware code much faster than compilation, so the user can have a quick response on *how the Signal Processing Algorithm implemented* in the firmware is working. In fact, it is possible to add some input to the simulation (like an external signal) and set probing points in the block diagram. In this way it is possible to *monitor the electrical signal* in that point.

*GTKWave* is an analysis tool used to perform debugging on Verilog or VHDL simulation models.

#### **Resource Explorer**

Sci-Compiler offers a *built-in tool*, called Resource Explorer, to connect supported boards and test the features of the FPGA firmware. This tool allows to manage all Local Bus readout blocks placed in the firmware diagram, therefore it gives the possibility *to read and write* the configuration registers (i.e. Signal Processing parameters) and *shows the readout instruments* like Spectrum, Oscilloscope, etc. in a GUI.

#### Measurement setup for testing digital processing system

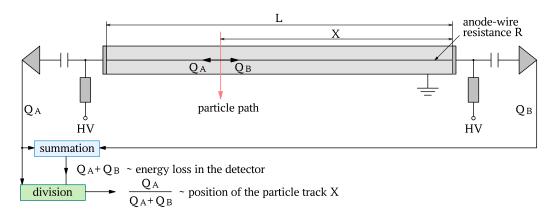

Helium-3-filled linear position-sensitive detectors (LPSDs) are based on the position-sensitive proportional counters design and have been widely applied to neutron scattering instruments owing to the high detection efficiency, the excellent neutron/gamma discrimination, and the ability to construct the detector with large area coverage.

Figure 9. Schematic diagram of position determination in a Helium-3 filled position sensitive proportional counters

| K                                                    |                               |                                                   | ризводственная фирма Консенсус<br>c-Production Firm CONSENSUS |        |  |

|------------------------------------------------------|-------------------------------|---------------------------------------------------|---------------------------------------------------------------|--------|--|

| <sup>3</sup> Не – счетчи<br><sup>3</sup> Не – neutro | ік медленных ней<br>n counter | Гелий–PSD–8/600–12,5/Л<br>Helium–PSD–8/600–12,5/L |                                                               |        |  |

| Effective length, mm                                 |                               | 586                                               | Own background, count/s                                       | 0.15   |  |

| <sup>3</sup> He pressure, atm                        |                               | 10                                                | Variation of sensitivity regarding the sample, %              | 5      |  |

| Operating voltage for proportional mode, V           |                               | 900                                               | Position resolution, mm                                       | 4 max* |  |

| Operating voltage for                                | PSD mode, V                   | 1350                                              | Anode resistance, Ohms/m                                      | 9400   |  |

| Peak width at half height, %                         |                               | 15 max                                            | Operation temperature range, °C                               | -50÷60 |  |

| Variation of the position of the mean value in a     | •                             | 15 max                                            | Weight, g                                                     | 37     |  |

\* - The position resolution essentially depends on the used measuring equipment.

This feature is taken from the Consensus website: *consensus-group.ru*

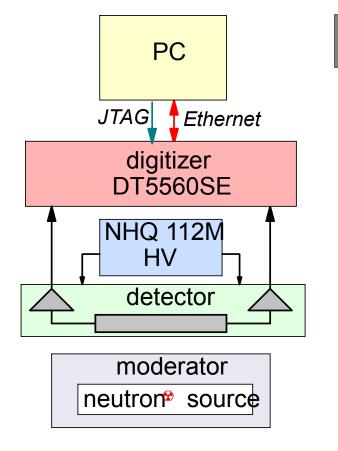

## Measurement setup for testing digital processing system

Figure 10. Block diagram connecting of installation

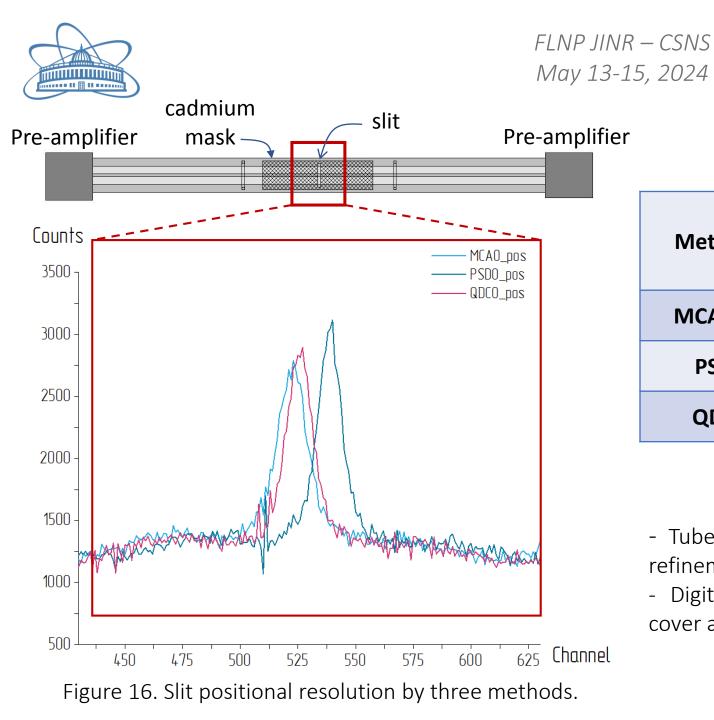

Figure 11. Schematic representation of the tubes and placement of a cadmium mask with a slide.

Figure 12. Part of a test setup with source, moderator and detector

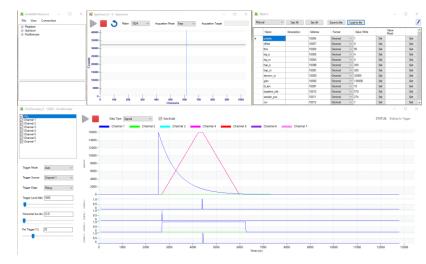

#### Program for measurement and testing digital processing system

9/16

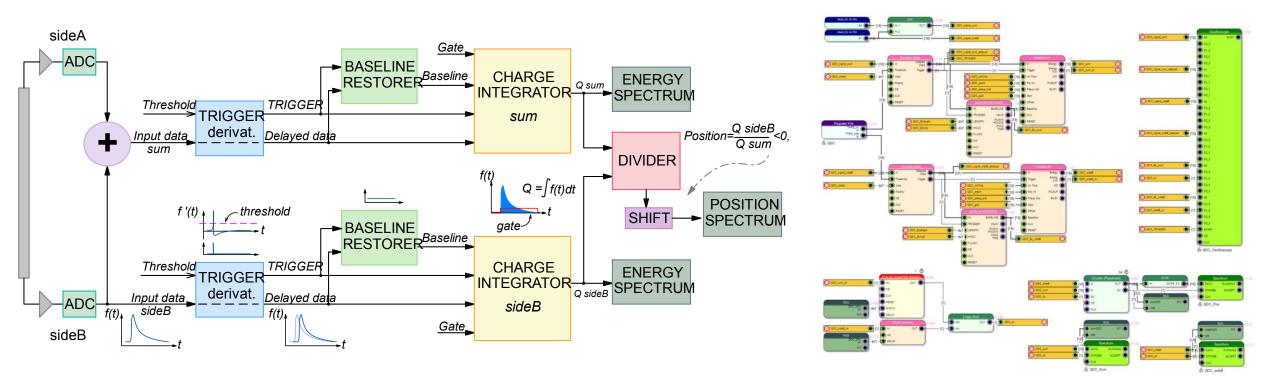

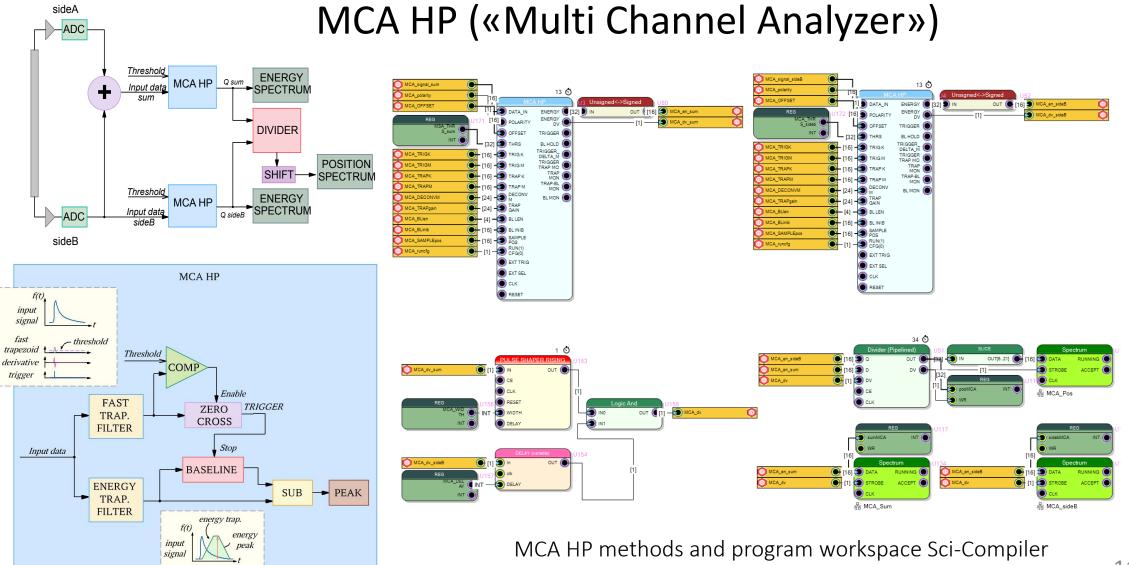

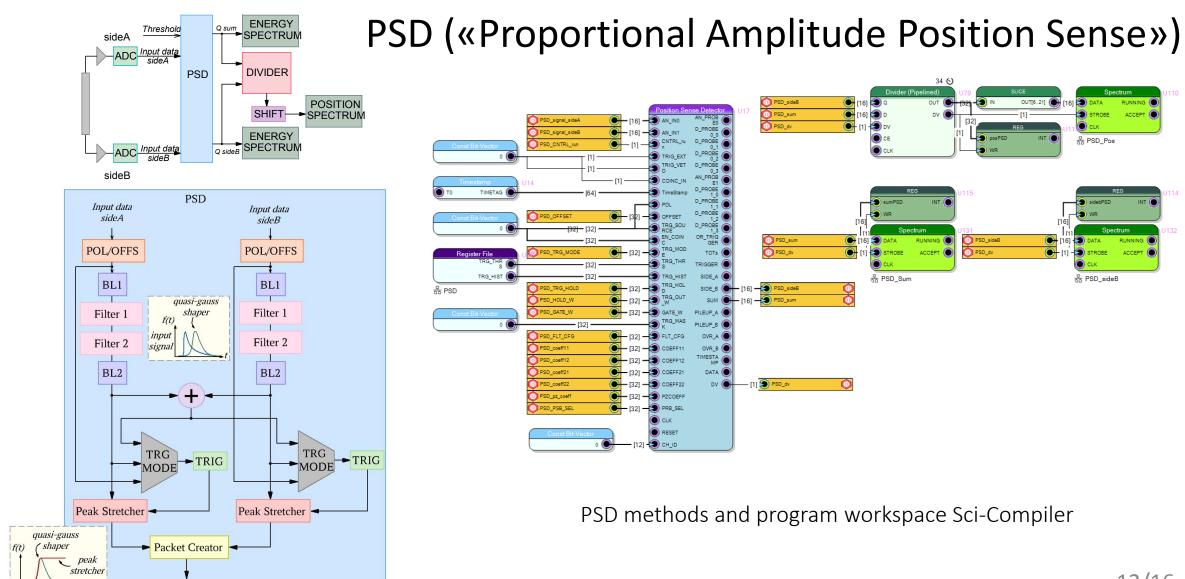

### QDC («Charge-to-Digital Converter»)

QDC methods and program workspace Sci-Compiler

11/16

Packet Data

FLNP JINR – CSNS May 13-15, 2024

FLnP

Table 1. Measurement results of the test system.

| Method | Dead time<br>methods, us | FWHM slit,<br>channel | Position<br>resolution, % |

|--------|--------------------------|-----------------------|---------------------------|

| MCA HP | 4,8                      | 15,7                  | 1,8                       |

| PSD    | 2                        | 12,7                  | 1,45                      |

| QDC    | 2                        | 13,8                  | 1,56                      |

#### Short summary:

- Tube measurements require more extensive analysis and refinement.

- Digitizer and FPGA programming software Sci-Compiler cover almost all needs for setting up an experiment.

#### Next steps.

- Implementation of list mode data transfer between hardware memory and PC using DMA (direct memory access) technology.

- Tests and measurements using specially developed software interfaces (see next slide).

- Optimization of all set of project parameters

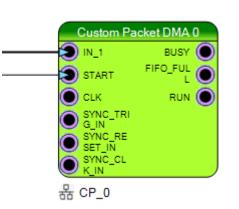

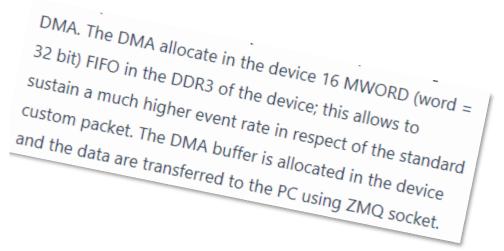

To speedup the data transfer in list mode, we use Custom Packet DMA SciCompiler IP.

Since all data transfer processes occur at the software level, Resource Explorer is no longer enough for us to set the parameters of this data transfer. We need our own software for this purpose.

| FLNP | JINR – | CSNS |

|------|--------|------|

| Мау  | 13-15, | 2024 |

|                        |                                | r 🥆 / F 🛱                          | ) {Å           | Run# 269                | ÷     |                  |     | project pa                   |

|------------------------|--------------------------------|------------------------------------|----------------|-------------------------|-------|------------------|-----|------------------------------|

| Plot Type S<br>TOF ~ C | tatistics Type<br>ChTrg Rate 🗸 |                                    |                | Apply                   |       |                  |     | parameters                   |

| Connect RunCtrl Ad     | cqMode HwPara                  | am HwComponents SwSpectr           | ums Statistics | Log                     |       |                  |     |                              |

| sel_SR                 | 1                              | MCA_SET.TRAPgain                   | 152000         | PSD_SET.PRB_SEL         | 3     | QDC_SET.BLlengh  | 8   | Diden                        |

| PWM_SR.period          | 2500000                        | MCA_SET.BLIen                      | 500            | PSD_SET.coeff11         | 14961 | QDC_SET.BLhold   | 400 | File FWupgrade GUI Mode      |

| PWM_SR.width           | 24000000                       | MCA_SET.BLinib                     | 100            | PSD_SET.coeff12         | 31311 | QDC_SET.INTIME   | 200 |                              |

| WINDOW.delay           | 500000                         | MCA_SET.SAMPLEpos                  | 200            | PSD_SET.coeff21         | 15137 | QDC_SET.PRE      | 0   |                              |

| WINDOW.gate            | 23000000                       | MCA_SET.runcfg                     | 1              | PSD_SET.coeff22         | 31477 | QDC_SET.PILEUP   | 400 |                              |

| Int_Time               | 125000000                      | MCA_SET.dv_sum_GATE                | 10             | PSD_SET.pz_coeff        | 262   | QDC_SET.GAIN     | 22  |                              |

| Int_Time_FIFOfull      | 125000000                      | MCA_SET.dv_sum_DELAY               | 0              | PSD_SET.output_baseline | 1     | QDC_0.THRS_sum   | 450 |                              |

| Permit_MCA             | 1                              | MCA_SET.dv_sideB_DELAY             | 10             | PSD_SET.second_filter   | 1     | QDC_0.THRS_sideB | 80  |                              |

| Permit_PSD             | 1                              | MCA_0.THRS_sum                     | 10             | PSD_SET.first_filter    | 1     | QDC_1.THRS_sum   | 450 | Plot Type Statistics         |

| Permit_QDC             | 1                              | MCA_0.THRS_sideB                   | 10             | PSD_SET.pole_zero       | 1     | QDC_1.THRS_sideB | 80  | TOF ~ ChTrg Rat              |

| MCA_selector           | 1                              | MCA_1.THRS_sum                     | 10             | PSD_SET.input_baseline  | 1     | QDC_2.THRS_sum   | 450 |                              |

| PSD_selector           | 1                              | MCA_1.THRS_sideB                   | 10             | PSD_SET.attenuation_2   | 7     | QDC_2.THRS_sideB | 80  | Connect RunCtrl AcqMode      |

| QDC_selector           | 1                              | MCA_2.THRS_sum                     | 10             | PSD_SET.attenuation_1   | 7     |                  |     |                              |

| MCA_SET.polarity       | 1                              | MCA_2.THRS_sideB                   | 10             | PSD_0.TRG_THRS          | 1000  |                  |     | ListMode                     |

| MCA_SET.OFFSET         | 0                              | PSD_SET.CNTRL_run                  | 1              | PSD_0.TRG_HIST          | 500   |                  |     |                              |

| MCA_SET.TRIGK          | 25                             | PSD_SET.OFFSET                     | 0              | PSD_1.TRG_THRS          | 1000  |                  |     | custom_package_use           |

| MCA_SET.TRIGM          | 25 Время н                     | арастания (risetime)<br>й трапеции | 3              | PSD_1.TRG_HIST          | 500   |                  |     | custom_package_acq_len       |

| MCA_SET.TRAPK          | 150                            | PSD_SET.TRG_HOLD                   | 0              | PSD_2.TRG_THRS          | 1000  | _                |     |                              |

| MCA_SET.TRAPM          | 220                            | PSD_SET.TRG_OUT_W                  | 1              | PSD_2.TRG_HIST          | 500   | _                |     | custom_package_acq_mode      |

| MCA_SET.DECONVM        | 31872                          | PSD_SET.GATE_W                     | 150            | QDC_SET.INIBIT          | 400   | _                |     | custom_package_timeout       |

|                        |                                |                                    |                |                         | ,     |                  |     | custom_package_thread        |

|                        |                                |                                    |                |                         |       |                  |     | custom_package_high_perform  |

|                        |                                |                                    |                |                         |       |                  |     | custom_package_threaded_buff |

|                        |                                |                                    |                |                         |       |                  |     |                              |

|                        |                                |                                    |                |                         |       |                  |     | custom_package_check_align_v |

|                        |                                |                                    |                |                         |       |                  |     | custom_package_data_processi |

| Status 🗿 Ready to s    |                                |                                    |                | Run 🔍                   |       |                  |     | custom_package_dma_buffer_s  |

**DIDEN** - software tool for DAQ and configuring all project parameters, including data transfer parameters between hardware memory and PC.

| 🔅 Diden                                              |                  |                         |         |       |  |  |  |  |  |

|------------------------------------------------------|------------------|-------------------------|---------|-------|--|--|--|--|--|

| File FWupgrade GUI Mode Help                         |                  |                         |         |       |  |  |  |  |  |

| DIDEN QMP2tubes_gen_CP           Version: 26-03-2024 |                  |                         |         |       |  |  |  |  |  |

| - ► ● • • • • • • • • • • • • • • • • • •            |                  |                         |         |       |  |  |  |  |  |

| Plot Type Statistics Type<br>TOF V ChTrg Rate V      | ]                |                         |         | Apply |  |  |  |  |  |

| Connect RunCtrl AcqMode HwPa                         | aram HwComponent | s SwSpectrums Statistic | s Log   |       |  |  |  |  |  |

| ListMode                                             | <u>H</u>         | lardwareSpectrums       |         | _     |  |  |  |  |  |

|                                                      |                  | spectrum_use            |         |       |  |  |  |  |  |

| custom_package_use                                   |                  | spectrum_rebin          | 0       | -     |  |  |  |  |  |

| custom_package_acq_len                               | 200000           | spectrum_min            | 0       | -     |  |  |  |  |  |

| custom_package_acq_mode                              | blocking ~       | spectrum_max            | 65535   |       |  |  |  |  |  |

| custom_package_timeout                               | 2000             | spectrum_limitmode      | freerun | ~     |  |  |  |  |  |

| custom_package_thread                                | false ~          | spectrum_limit          | 0       |       |  |  |  |  |  |

| custom_package_high_performance                      | false ~          | 1                       |         |       |  |  |  |  |  |

| custom_package_threaded_buffer_size                  | 150000           | _                       |         |       |  |  |  |  |  |

| custom_package_check_align_word                      | true ~           | oscilloscope_use        |         |       |  |  |  |  |  |

| custom_package_data_processing                       | raw ~            | 1                       |         |       |  |  |  |  |  |

| custom_package_dma_buffer_size                       | 200000           | mcratemeter_use         |         |       |  |  |  |  |  |

|                                                      |                  |                         |         |       |  |  |  |  |  |

Figure 17. DIDEN – FLNP software for OpenFPGA-based projects (DAQ and flexible configuration). 15/16

## Conclusion:

In my statement, I showed the main stages of the project development for signal processing of a helium-3-filled position-sensitive detector.

The methods of signal processing from such detectors are considered, the known feature of which is high and unstable rise time of signals, so for each series of detectors it is necessary to select the optimal method of signal processing from this detector.

FLNP JINR – CSNS Workshop on the neutron scattering technology and multi-disciplinary research International Conference Centre, Dubna

## Thank you for your patience!

Speaker: electronics engineer Department of spectrometer complex IBR-2 FLNP JINR *Anastasiya Kazliakouskaya nasta94@jinr.ru*

> FLNP JINR – CSNS May 13-15, 2024