# STT FE Electronics Update

## VMM Amplifier & Shaper

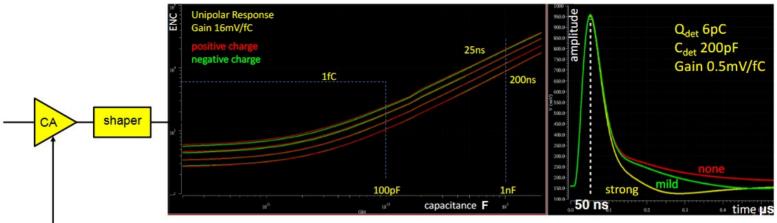

- Input transistor: PMOS 180 nm x 20 nm, 3 stage amplifier,

- 2 stages used for adjustable gain: 0.5, 1, 3, 4.5, 6, 9, 12, 16 mV/fC

- 1 for adjustable charge polarity: positive or negative

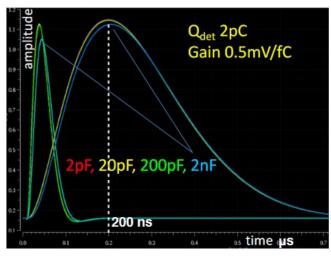

- Input capacitance: can operate from sub-pF to several nF

- Maximum charge: 2 pC in linear range, fast recovery from 50 pC

- Semi gaussian DDF c-shaper 3rd order

- Configurable ion tail suppression: none, mild or strong

- Adjustable peaking time: 25, 50, 100, 200 ns

- Leakage-adaptive, BGR-stabilised baseline

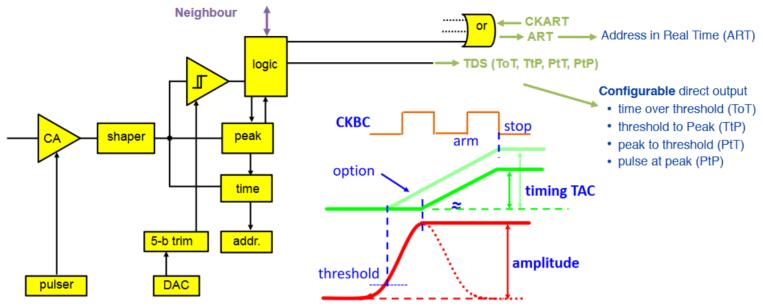

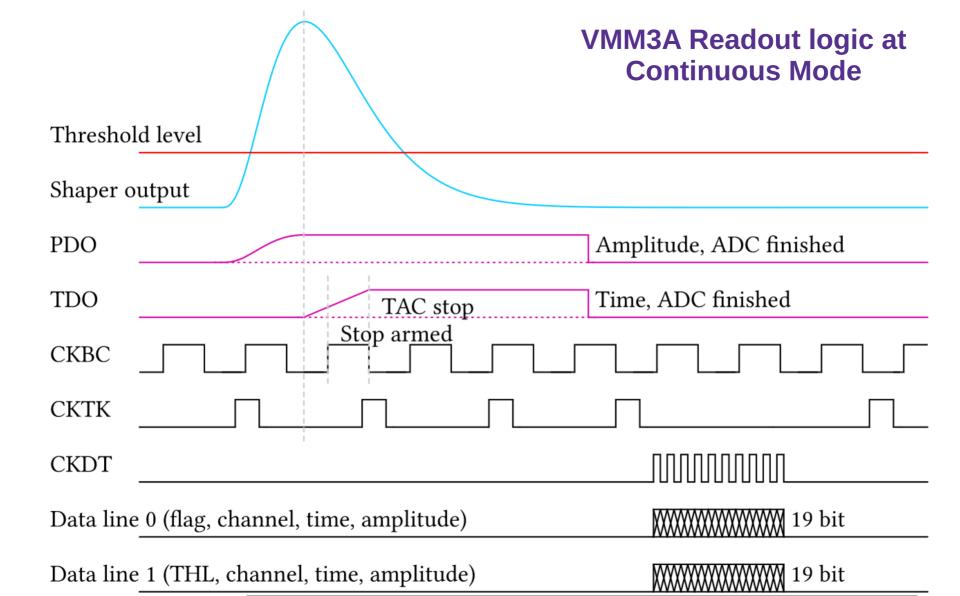

# VMM3a Discrimination, Charge and Time

- Global 10-bit DAC for adjusting the threshold Discrimination with sub-hysterisis (effective 2mV)

- Adjustable **5-bit discrimination** threshold **per channel** to adjust at ~mV level

- Neighbour logic to trigger sub-threshold channels with inter-chip communication

- Configurable direct output per channel and serial fast output of address as an OR of all channels

- · Peak detection: measurement of peak amplitude and storage in analog memory

- Time detection: measurement of peak/threshold timing through a configurable time to amplitude converter (TAC: 60, 100, 350, 650 ns) and storage in analog memory

- Clock working mode on synchronous machines but also as strobe for asynchronous operations

First FEB prototype, as well as existing Mu2E board and SRS Hybrid boards was tested at several SPS Testbeams and in the lab. Issues were found.

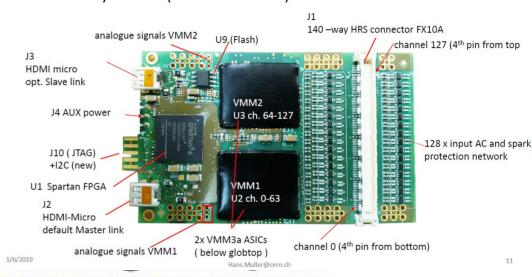

#### VMM hybrid (V4.0 2020)

# Channels latch at T@T mode (VMM3A)

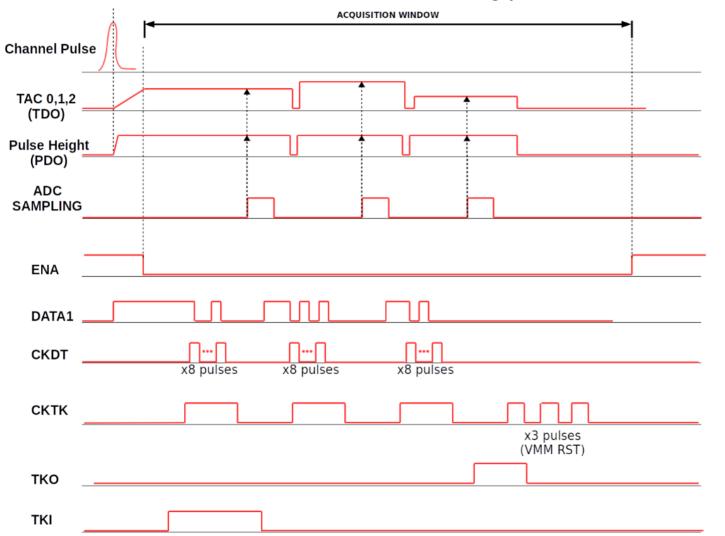

The VMM3/3A has alternative «External ADC» Mode which should handle both saturation issue, channel latching problem and ADC resolution

complete the ASIC can be switched readout phase.

The first set of amplitude and time voltages is made

Once the process is

available at the analog

outputs. The address of

the channel is serialised

and made available at the

digital output using six data

clocks.

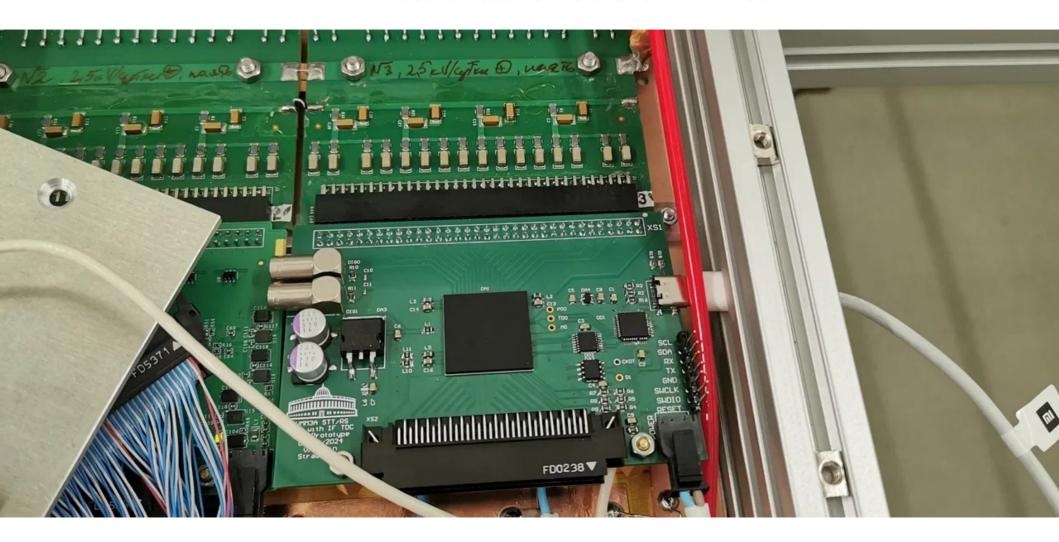

A **new FEB** based on **VMM3A** has been developed and assembled. It uses «new» external ADC Mode with **12-bit 4MSPS ADC**. First results on next slides. Testing is ongoing.

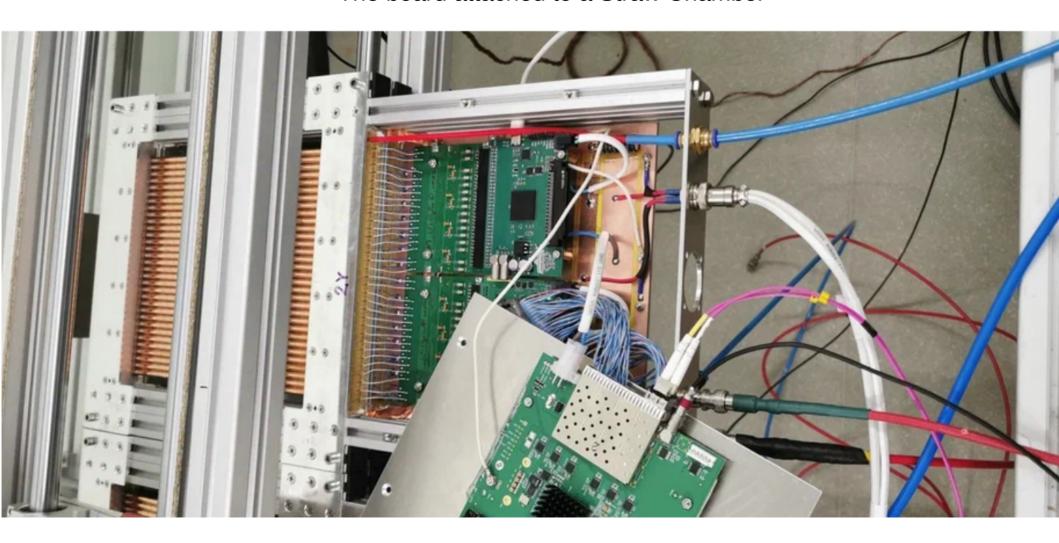

#### The board attached to a Straw Chamber

## The board attached to a Straw Chamber

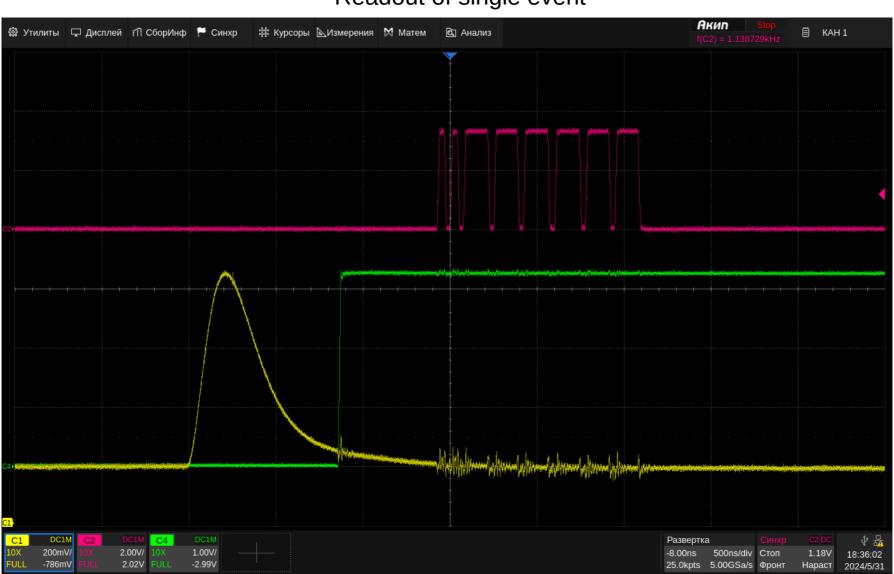

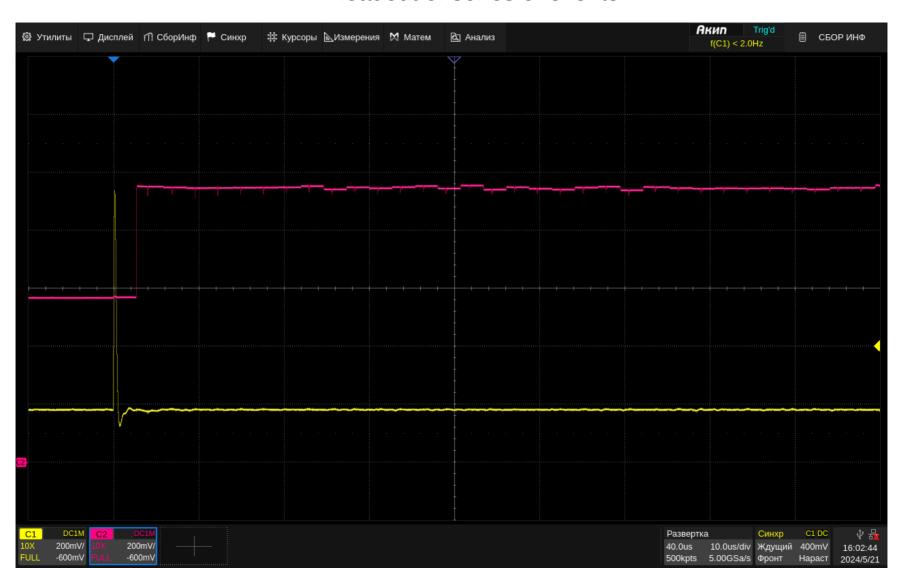

# Readout of single event

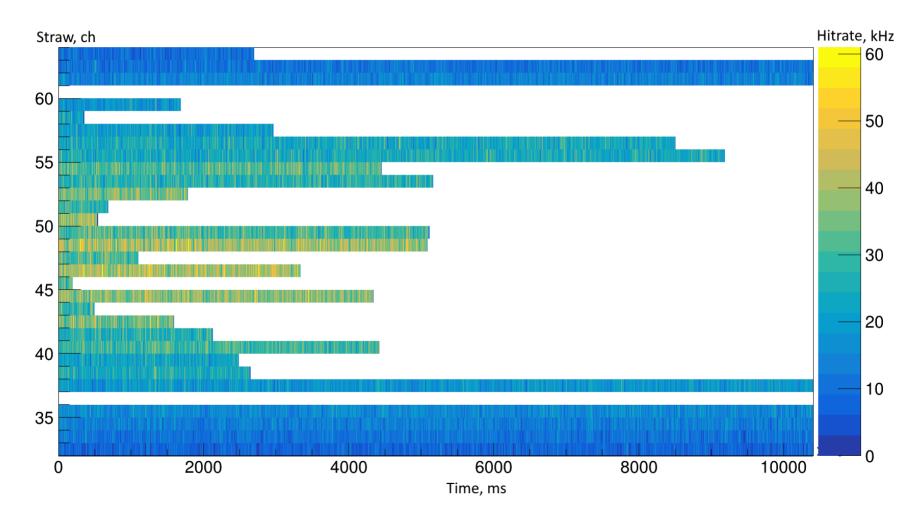

#### Readout of series of events

#### VMM3/3A has well known bad ADC/TDC perfomance in standard Continuous Mode

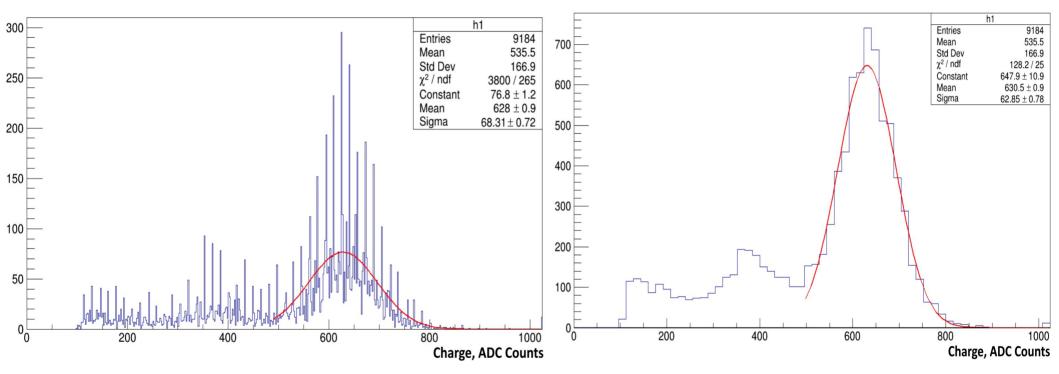

Fe55 Spectra, internal ADC

Fe55 Spectra, internal ADC Hard rebin applied

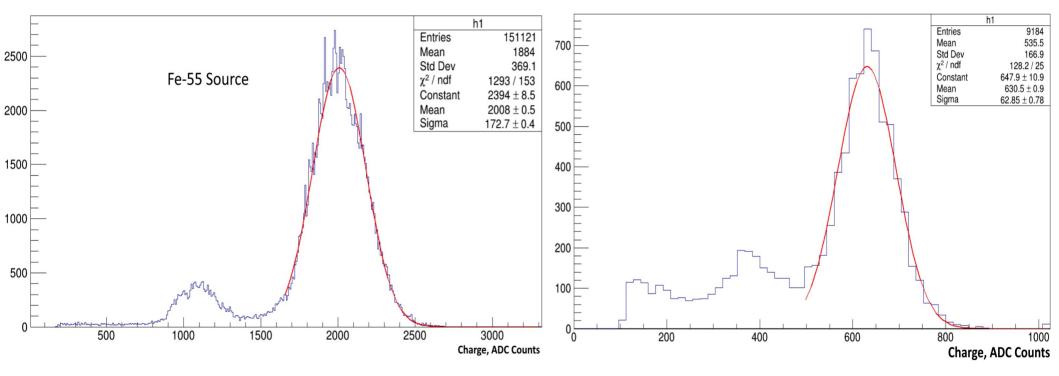

#### VMM3/3A has well known bad ADC/TDC perfomance in standard Continuous Mode

Fe55 Spectra, external ADC Much better resolution

Fe55 Spectra, internal ADC Hard rebin applied

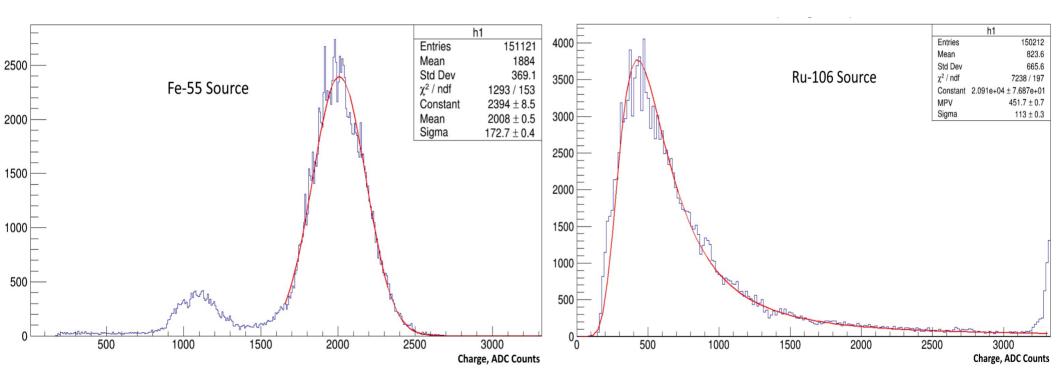

#### VMM3/3A has well known bad ADC/TDC perfomance in standard Continuous Mode

Fe55 Spectra, external ADC Much better resolution

Ru106 Spectra, external ADC Much better resolution

# Some current summary:

- «New» external ADC mode has been tested

- Much better ADC perfomance observed

- Still have some ADC issues, so new ADC is to be chosen

- Rate perfomance of the whole system to be tested

- Time resolution and PLL stability to be tested

- L1 interface logic to be implemented

# **Backlog**

### Table 1. ADC features on STM32G4 Series

| Features                 | Values for STM32G4 Series                                                                                                                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of ADCs           | Up to 5                                                                                                                                                                                                |

| Resolution               | 12 bits (or 10, 8, 6 bits), 16 bits with oversampling                                                                                                                                                  |

| Number of input channels | Up to 42                                                                                                                                                                                               |

| ADC principle            | Successive approximation register (SAR)                                                                                                                                                                |

| ADC clock frequency      | Up to 60 MHz (up to 52 MHz in multiple-ADC operation case)                                                                                                                                             |

| Sampling rate            | Up to 4 Msps (up to 3.46 Msps in multiple-ADC operation case)                                                                                                                                          |

| Sampling time            | 2.5 to 640.5 [ADC clock periods]                                                                                                                                                                       |

| Supply voltage           | V <sub>DDA</sub> = 1.62 V to 3.6 V                                                                                                                                                                     |

| Reference voltage        | On dedicated VREF+ $pin^{(1)}$ (internal or external), $V_{REF+}$ = 1.62 V to $V_{DDA}$ (see datasheet)                                                                                                |

| Triggers                 | From external pins or internal peripherals (timers)                                                                                                                                                    |

| Conversion modes         | Single, continuous, scan-selected channels, discontinuous mode                                                                                                                                         |

| Others                   | Offset calibration, analog watchdog, hardware oversampling, offset compensation, gain compensation, interleaved mode (two ADCs coupled), sampling time controlled by trigger edges, bulb mode sampling |

1. In the LQFP128-pin packages, two VREF+ pins are available.

| Compare | Mfr Part #    |                                                                    | Quantity<br>Available ⑦                | Price               | Price                                                          |         | Package                                         | Product Status | DigiKey Programmable | Core Processor      | Core Size                 | Speed  | Connectivity                                                           | Peripherals                                                              |

|---------|---------------|--------------------------------------------------------------------|----------------------------------------|---------------------|----------------------------------------------------------------|---------|-------------------------------------------------|----------------|----------------------|---------------------|---------------------------|--------|------------------------------------------------------------------------|--------------------------------------------------------------------------|

|         | ^             | Ÿ                                                                  | ^ ~                                    | ^                   | ~                                                              | ^ ~     | ^ ~                                             | ^ ~            | ^ ~                  | ^ ~                 | ^ ~                       | ^ ~    | ^                                                                      | ^ ~                                                                      |

|         |               | STM32F030R8T6 Mainstream Arm Cortex-M0 Value I STMicroelectronics  | <b>209,65</b><br>In Sto                |                     | : <b>\$2.86000</b><br>Tray                                     | STM32F0 | Tray ⑦                                          | Active         | Not Verified         | ARM®<br>Cortex®-M0  | 32-Bit<br>Single-<br>Core | 48MHz  | I <sup>2</sup> C, SPI,<br>UART/USART                                   | DMA, POR,<br>PWM, WDT                                                    |

|         | D O           | STM32G030K8T6 IC MCU 32BIT 64KB FLASH 32LQFP STMicroelectronics    | <b>103,55</b><br>In Sto                |                     | : <b>\$1.96000</b><br>Tray                                     | STM32G0 | Tray ⑦                                          | Active         | Not Verified         | ARM®<br>Cortex®-M0+ | 32-Bit<br>Single-<br>Core | 64MHz  | I <sup>2</sup> C, IrDA,<br>LINbus, SPI,<br>SmartCard,<br>UART/USART    | DMA, I <sup>2</sup> S,<br>POR, PWM,<br>WDT                               |

|         | D<br>Q        | STM32G030F6P6 IC MCU 32BIT 32KB FLASH 20TSSOP STMicroelectronics   | <b>94,49</b><br>In Stor                |                     | : <b>\$1.61000</b><br>Tray                                     | STM32G0 | Tray ⑦                                          | Active         | Not Verified         | ARM®<br>Cortex®-M0+ | 32-Bit<br>Single-<br>Core | 64MHz  | I <sup>2</sup> C, IrDA,<br>LINbus, SPI,<br>SmartCard,<br>UART/USART    | DMA, I <sup>2</sup> S,<br>POR, PWM,<br>WDT                               |

|         |               | STM32G474CBT6 Mainstream Arm Cortex-M4 MCU 170 STMicroelectronics  | In Stor<br><b>82,5</b> 0<br>Marketplar | k<br><b>0</b> 1,500 | ) : <b>\$4.13999</b><br>Tray<br>) : <b>\$3.15000</b><br>Tray   | STM32G4 | Tray ⑦ Tray ⑦                                   | Active         | Not Verified         | ARM®<br>Cortex®-M4F | 32-Bit<br>Single-<br>Core | 170MHz | CANbus, I <sup>2</sup> C,<br>IrDA, LINbus,<br>QSPI, SPI,<br>UART/USART | Brown-out<br>Detect/Reset,<br>DMA, I <sup>2</sup> S,<br>POR, PWM,<br>WDT |

|         | <b>&gt;</b> Ø | STM32L071CZT6TR IC MCU 32BIT 192KB FLASH 48LQFP STMicroelectronics | <b>78,58</b><br>In Sto                 | k 2,400             | : \$5.34000<br>Cut Tape (CT)<br>): \$2.67868<br>pe & Reel (TR) | STM32L0 | Tape & Reel (TR) ⑦ Cut Tape (CT) ⑦ Digi-Reel® ⑦ | Active         | Not Verified         | ARM®<br>Cortex®-M0+ | 32-Bit<br>Single-<br>Core | 32MHz  | I <sup>2</sup> C, IrDA, SPI,<br>UART/USART                             | Brown-out<br>Detect/Reset,<br>DMA, I <sup>2</sup> S,<br>POR, PWM,<br>WDT |

|         |               | STM32G031K8U6 IC MCU 32BIT 64KB FLASH 32UFQFPN STMicroelectronics  | <b>66,38</b><br>In Sto                 |                     | : <b>\$2.86000</b><br>Tray                                     | STM32G0 | Tray ①                                          | Active         | Not Verified         | ARM®<br>Cortex®-M0+ | 32-Bit<br>Single-<br>Core | 64MHz  | I <sup>2</sup> C, IrDA,<br>LINbus, SPI,<br>SmartCard,<br>UART/USART    | Brown-out<br>Detect/Reset,<br>DMA, I <sup>2</sup> S,<br>POR, PWM,<br>WDT |

|         |               | STM32L071CZY6TR<br>IC MCU 32BIT 192KB FLASH<br>49WLCSP             | <b>57,01</b><br>In Sto                 | k                   | : \$5.23000<br>Cut Tape (CT)                                   | STM32L0 | Tape & Reel (TR) ① Cut Tape (CT) ②              | Active         | Not Verified         | ARM®<br>Cortex®-M0+ | 32-Bit<br>Single-         | 32MHz  | I <sup>2</sup> C, IrDA, SPI,<br>UART/USART                             | Brown-out<br>Detect/Reset,                                               |