# Status of the HGND readout development and integration in the BM@N DAQ.

**D. Finogeev**, F. Guber, A. Izvetnyy, S. Musin, D. Serebryakov INR RAS, Moscow

### Acknowledgements:

This work was carried out at the Institute for Nuclear Research, Russian Academy of Sciences, and supported by the Russian Scientific Foundation grant  $N^2$ 2-12-00132.

### Outline

- HGND readout topology

- 100ps FPGA based TDC

- Status of the FPGA firmware development

- Status of the readout board development

- Status of the DCS & readout software architecture

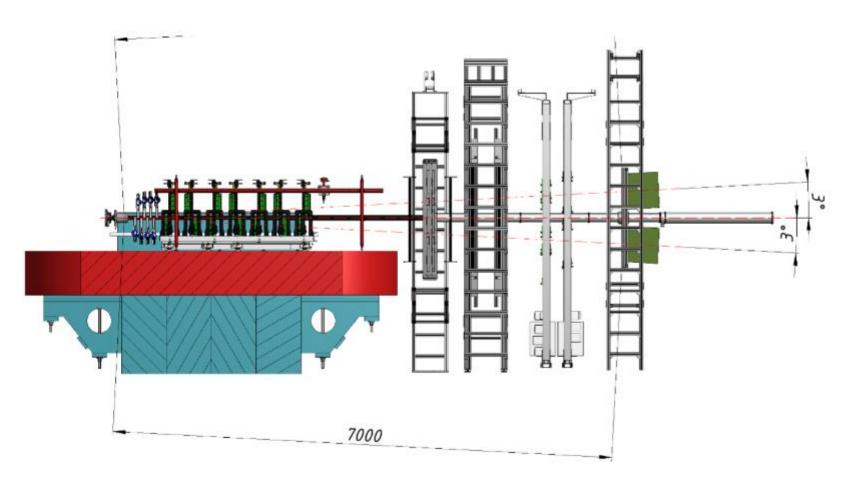

# Detector arrangement

- Detector for highenergy neutron flow measurement

- ToF method with T0 as the "start" signal source

- 7m measurement distance

- Detector is split into 2 "blocks" for improved acceptance

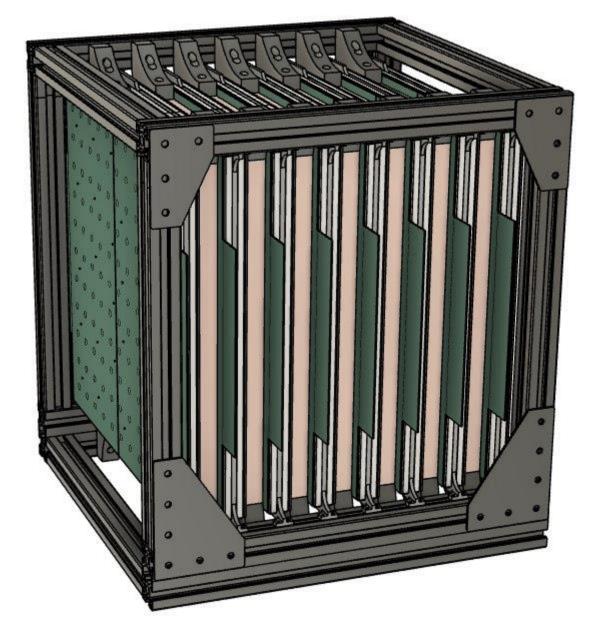

# Detector "block"

- Each block consists of:

- A VETO-layer

- 8 Cu absorbers

- 8 sensitive layers

- 11x11 grid of scintillatiors each

- Assembly is light-tight and aircooled

- Framing is built with light-weight Al profiles

### FEE & readout architecture

16 layers with scintillation matrix 11X11 16 LED boards 32 FEE boards **READOUT** 8 Readout boards FPGA TDC: 84 CH FPGA#1 BOARD LED BOARD 3 FPGA per board SLAVE 84 channels per FPGA 125 MHz duplex LVDS line: clock LED 2000 channels in total dataflow / control FPGA TDC: 84 CH FPGA#2 SLAVE FEE BOARD FPGA TDC: 84 CH DAC / DCS MPPC SFP- IPbus FPGA#0 MASTER TRIGGER: LVTTL, 50Ω, LEMO SFP - White SYNC Rabbit PTC SPI DAC AD5662 FEE board White Rabbit: 3.3 V 4-ch Voffset DAC, VCXO, PLL MCU regulator MAX31865 48 V PSU Readout board

PCIe connector

# Readout & trigger

- 100 ps TDC is implemented in Kintex 7 FPGA, 84 channels per FPGA chip (2000 total)

- White Rabbit (WR) is used for event's time synchronization (8 links total):

- TDCs use clock sourced from WR synchronous to whole BM@N

- o WR timestamps are assigned to measured events

- Ethernet UDP protocol (*IPbus* [1]) is used for data forwarding and board control

- Local network connect readout boards (8 ethernet links) with FLP

- The maximum HGND channel load is 3 kHz. The event size is 7x16 bits. The upper limit per link is not exceed *100 Mbit/s*. *The continuous readout* is implemented without busy signal.

- The trigger is processed on FLP site:

- o Trigger signal is connected to TDC channel and digitized with WR timestamp in FPGA

- o Message trigger accompanied by a timestamp is transmitted to FLP for event selection

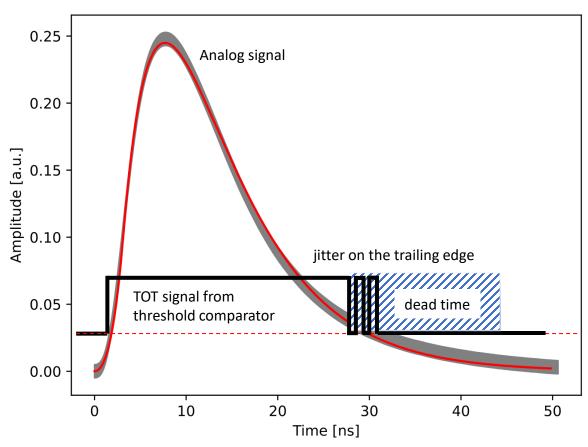

# TDC Time Over Threshold (TOT)

- The threshold is tunable around 20 mV

- Signals length range is 20 60 ns

- Signals less than 6.4 ns are rejected for noise reduction

- Dead time is tunable in range 30 200 ns for comparator jitter filtering

- Minimum TOT time and dead time available in FPGA TDC are 3.2 ns

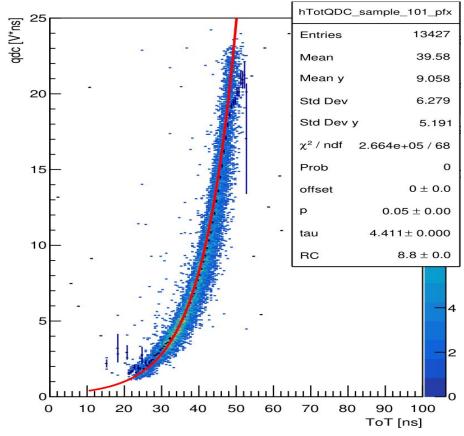

### Amplitudes vs TOT time with analytical forecast

- TOT amplitude resolution is in range 14 22%

- Is used for time slewing correction

[2] N. Karpushkin, D. Finogeev, F. Guber, D. Lyapin, A. Makhnev et al., Analytical description of the time-over-threshold method based on time properties of plastic scintillators equipped with silicon photomultipliers, DOI: 10.1016/j.nima.2024.169739

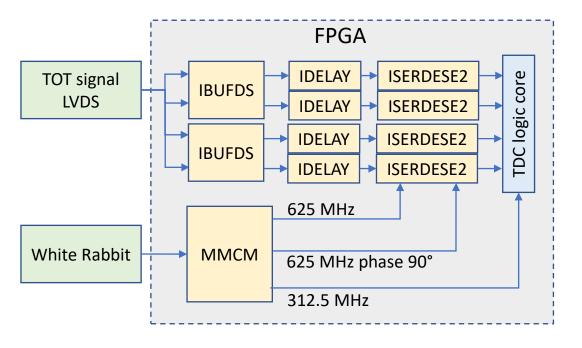

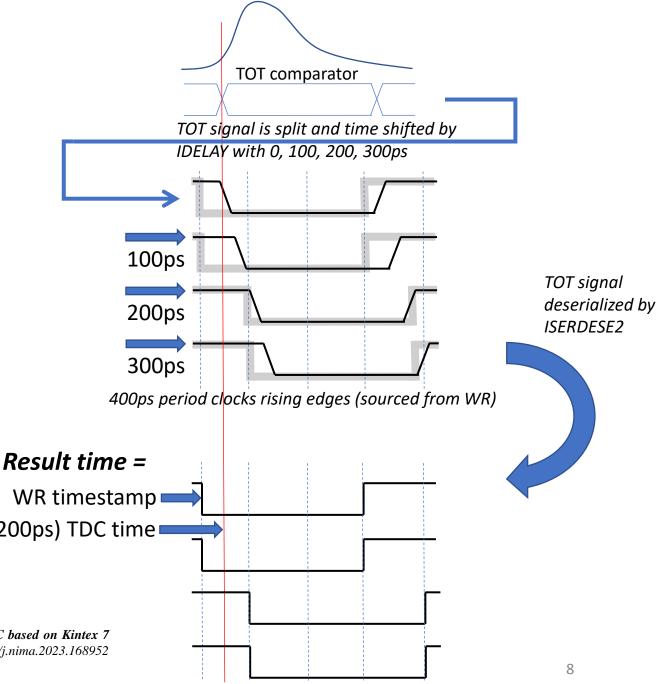

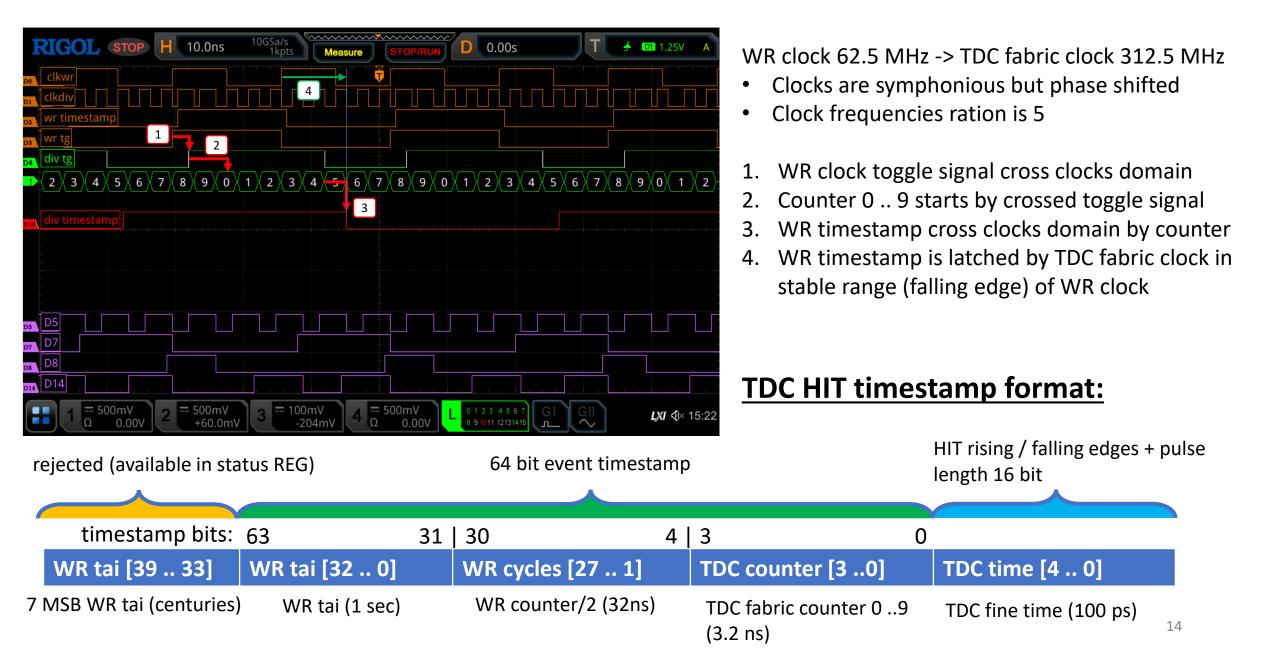

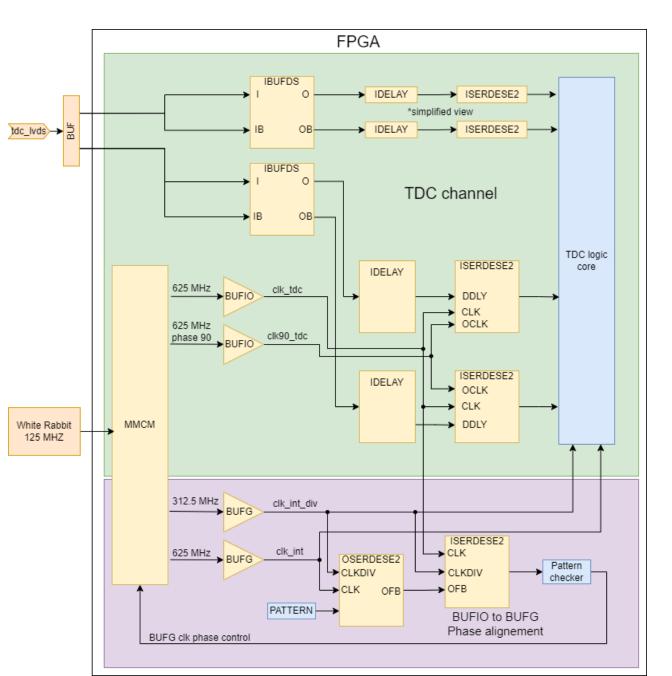

# The 100ps FPGA TDC principle of operation

The TDC is <u>based on the Kintex-7</u> input serial-to-parallel converter with oversampling capability and programmable delay. The design is <u>based on Xilinx recommendations</u>, and + (200ps) TDC time uses <u>only documented features</u> of the FPGA within its specifications.

[3] D. Finogeev, F. Guber, A. Izvestnyy, N. Karpushkin, A. Makhnev et al., *Development of 100 ps TDC based on Kintex 7 FPGA for the High Granular Neutron Time-of-Flight detector for the BM@N experiment*, *DOI: 10.1016/j.nima.2023.168952*

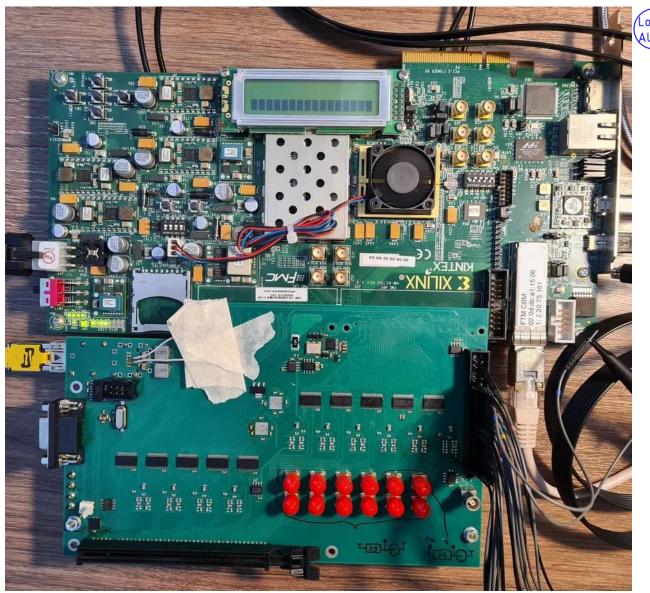

# HGND readout v2 prototype (39 channels)

based on the Kintex 7 evaluation board (KC705)

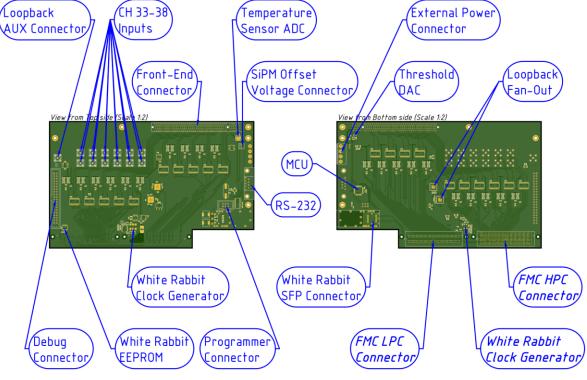

- Addon for Kintex 7 evaluation board

- 33 PCIe + 6 SMA TDC channels

- Ethernet readout

- White Rabbit synchronization

- FPGA loopback for TDC calibration

- Readout board functionality:

- PCIe connector for scintillation matrix, Temperature sensor, SiPM offset voltage control DAC threshold

# The FPGA TDC time scan results

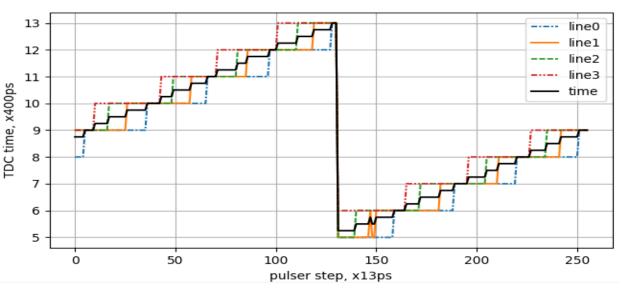

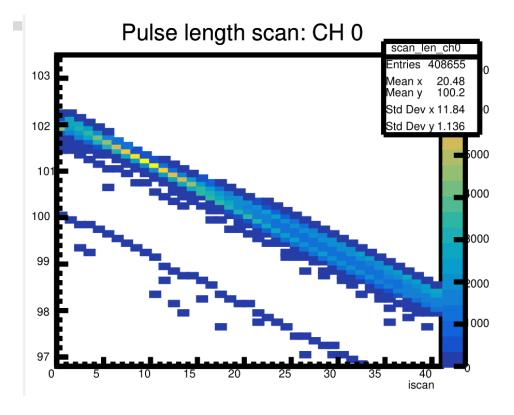

Four TDC lines and the resulting time dependence on the pulse time shift are shown. Pulses are generated by FPGA MMCM synchronously to the TDC clock with a phase step of 12.9ps. The single scan pass was taken with a digital FPGA logic analyzer.

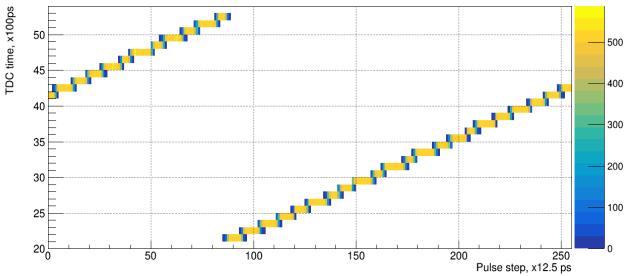

The TDC time dependence on pulse time shift. Pulses are generated by FPGA MMCM synchronous to TDC clock, and the time step is 12.9 ps. Data was taken with PC readout, 1000 events per single time shift step.

# New FPGA TDC alignment procedure

# TDC alignment v1 (FPGA): lines alignment algorithm

# TDC alignment v2 (Software emu): delays enumeration + density code test

- New algorithm of TDC lines delay calibration was developed.

- Based on delays enumeration with code density test for verification.

- Requires minimum FPGA resources

- Working with raw TDC data in software for algorithms simulation.

- ☐ Will be implemented in FPGA TDC for auto-calibration procedure.

- ☐ The optimal delay step value should be found

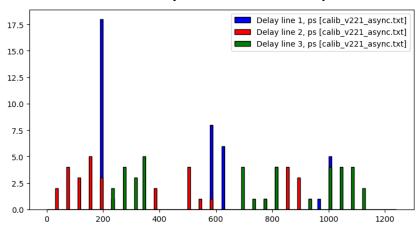

### TDC lines delays distribution, ps

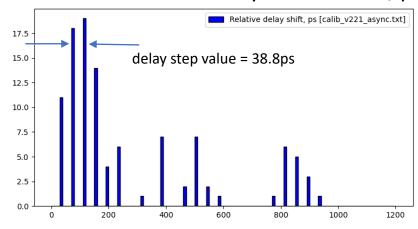

### TDC lines relative delays distribution, ps

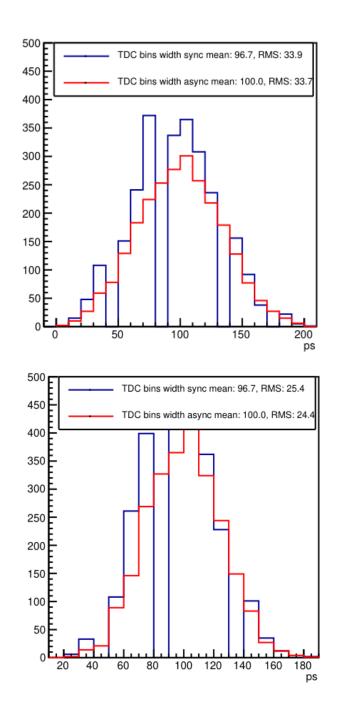

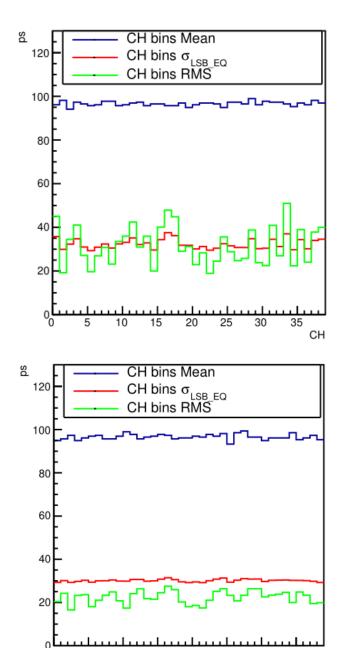

# The FPGA TDC test results

### PROTO\_V2

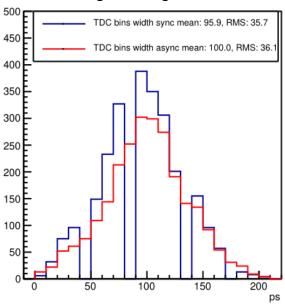

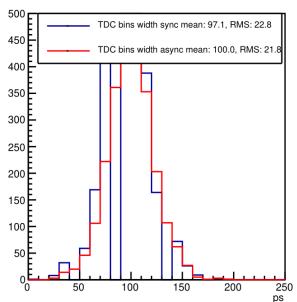

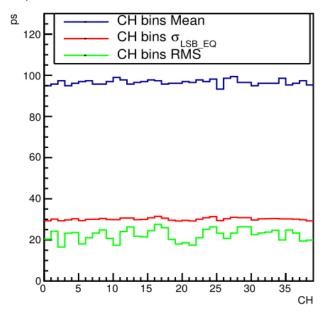

TDC bins with for all 39 channels: mean value, RMS, equivalent LSB precision. Calculated with synchronous scan

### The equivalent LSB precision is ~30ps.

$$LSB_{EQ} = \sqrt{\frac{1}{\sum_{i=0}^{i=N-1}BinWidth[i]}} \cdot \sum_{i=0}^{i=N-1}BinWidth^{3}[i]$$

$$\sigma_{LSB\_EQ} = \frac{LSB_{EQ}}{\sqrt{12}} / \sqrt{\frac{BinWidth[\forall i]}{\sigma_{LSB\_EQ}}} = \frac{100ps}{29ps}$$

[4] N. Lusardi et al., "Quantization noise in non-homogeneous calibration table of a tcd implemented in fpga," DOI:10.1109/NSSMIC.2014.7431149

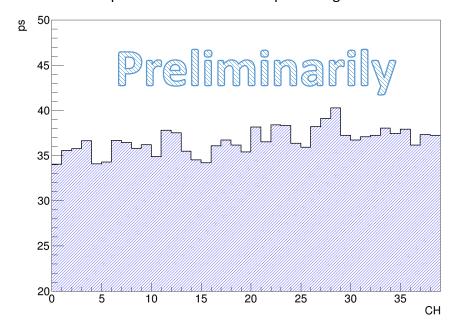

PROTO\_V2

TDC bins precision measured with pulse length 101.2ns

The measured TDC precision is 35 – 40 ps.

The time resolution of the scintillation cell is 130 ps

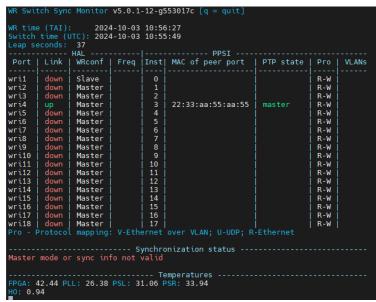

# **HGND** White Rabbit synchronization

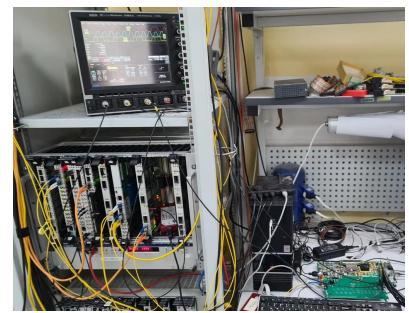

HGND WR test setup at INR (Moscow) with provided WR switch

```

WR PTP Core Sync Monitor wrpc-v4.2-19-q54d3079

Thu, Oct 3, 2024, 10:55:12

wru1: Link up (RX: 106, TX: 45) IPv4: 192.168.1.5 (static assignment)

Locked Calibrated

PTP status: slave

Synchronization status:

TRACK PHASE

enabled

Aux clock 0 status:

Timing parameters:

910354 ps

Master-slave delay:

442861 ps

220857 ps, RX:

245547 ps

0 ps, RX:

Total link asymmetry:

24632 ps

443950 ps

Cable rtt deláy:

hase setpoint:

10358 ps

1 ps

wrc#

```

**HGND WR node monitor**

WR master switch monitor

### WR synchronization works:

- ✓ WR switch connected

- ✓ The issue reason was wrong FIFO instance file version (for Virtex 6)

- ☐ WR design update to the latest v5.0 (optional)

# White Rabbit timestamp synchronization with FPGA TDC

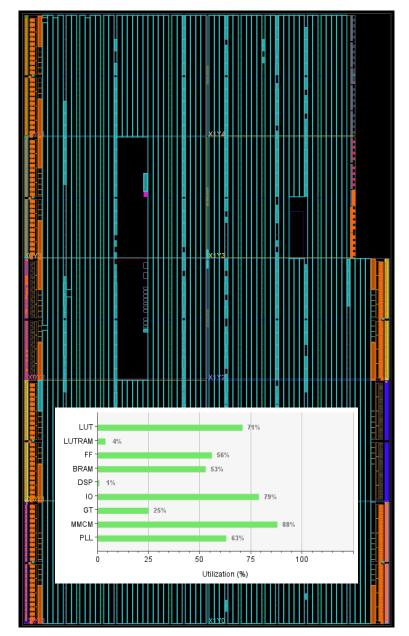

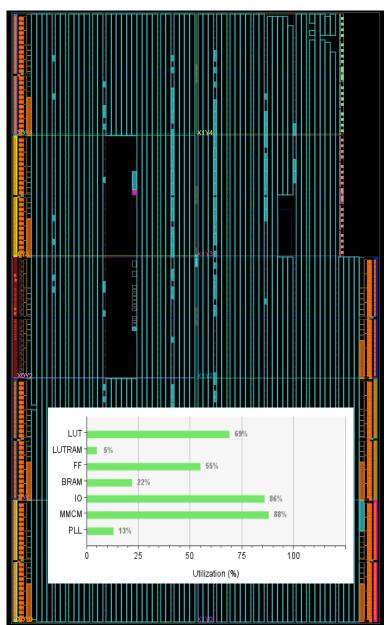

# Full scale FPGA design

### Master FPGA 72 ch

### Slave FPGA 84 ch

- Master & Slave FPGA firmware are compiled

- Usable for PCB pinout verification

- TODO list:

- ☐ Control registers optimization

- **☐** TDC revision

- ☐ FPGA cross link implementation

### **HGND** readout board routing status:

### May 2024:

- ✓ Front-End connectors pinout and schematic

- ✓ White Rabbit periphery schematic

- Board geometry and connector positions (May 2024)

- Power supply schematic (June-July 2024)

- ☐ TDC tests with prototype v2 (June July 2024)

- ☐ FPGA pinout and schematic (June-July 2024)

- Board routing (August-September 2024)

### Sep 2024:

- ✓ Front-End connectors pinout and schematic

- ✓ White Rabbit periphery schematic

- ✓ Board geometry and connector positions (May 2024)

- ✓ Power supply schematic (June-July 2024)

- ✓ TDC tests with prototype v2 (June July 2024)

- ✓ FPGA pinout and schematic (June-July 2024)

- Board routing (August-November 2024)

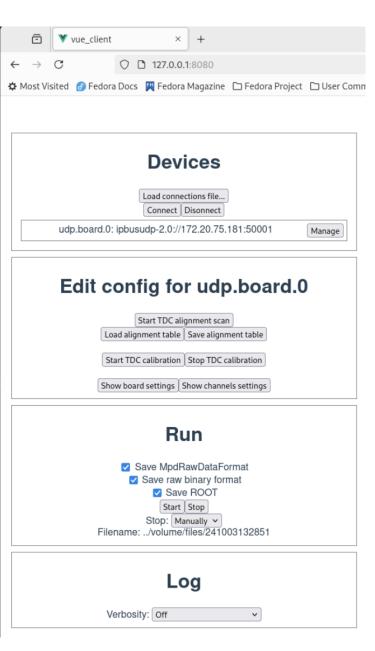

### **HGND** readout & DCS readout test setup

### Synthetic tests for proving the concept of developed software architecture

- ✓ Data & trigger FPGA emulator

- √ 400 Mbit/s data readout per board (100 Mbit is required)

- √ 800 Mbit/s readout rate with 2 boards was achieved (is the estimated rate for HGND with 8 links)

- ✓ Data sorting by trigger selection with two links readout: data rate 2.6 MHz (10 kHz/channel), trigger rate 10kHz.

- ✓ Data flow (soft emu) & DCS commands test on BM@N FLP

- Preparing software for TDC tests

- Working on GUI filling and debugging

## Conclusions

- Status of the HGND readout development:

- ✓ Basic TDC tests was performed with 33 channels prototype

- ✓ The White Rabbit synchronization works

- ✓ Full scale FPGA design was prepared (dummy)

- ✓ Readout & DCS software is ready (basic)

- ➤ Continue tests with prototype v2 (cosmic and beam tests with matrix, TDC development)

- ➤ Working on the FPGA firmware: TDC revision, cross FPGA link routine

- ➤ Working on the design of the full scale readout board: board routing

- Software debugging and updates

Thank you for your attention!

# **BACKUP**

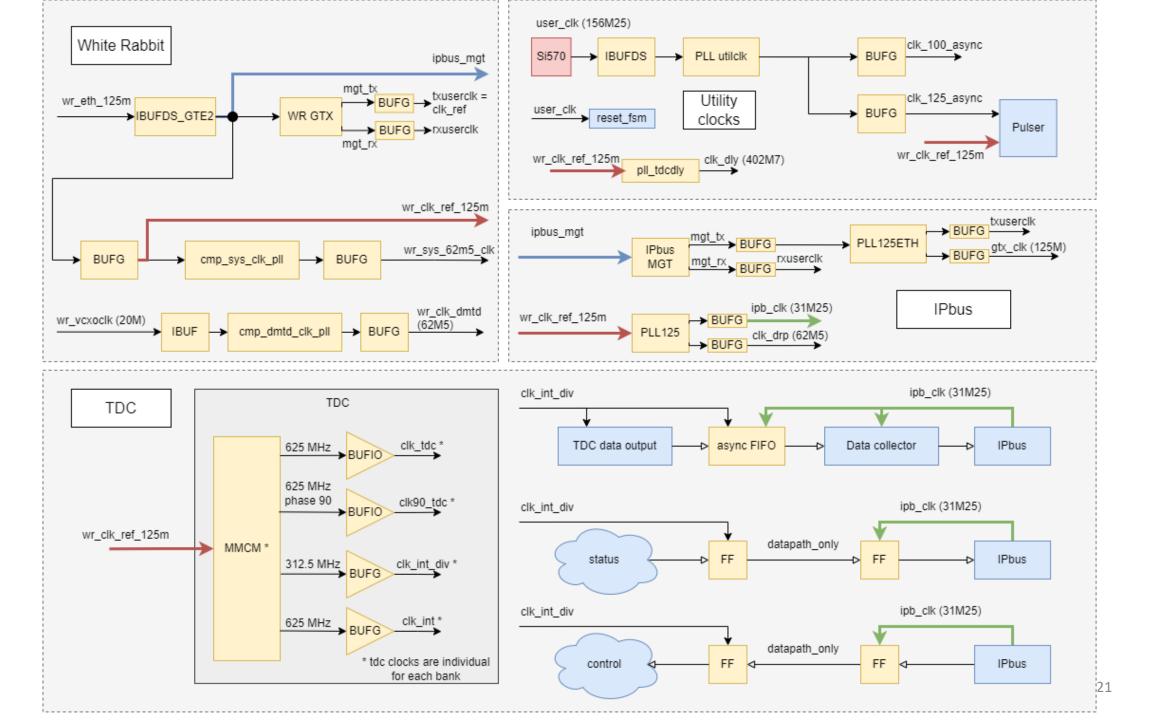

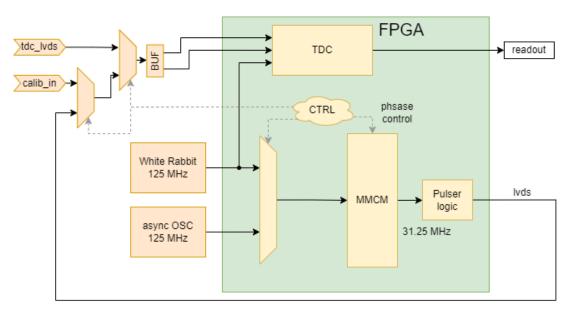

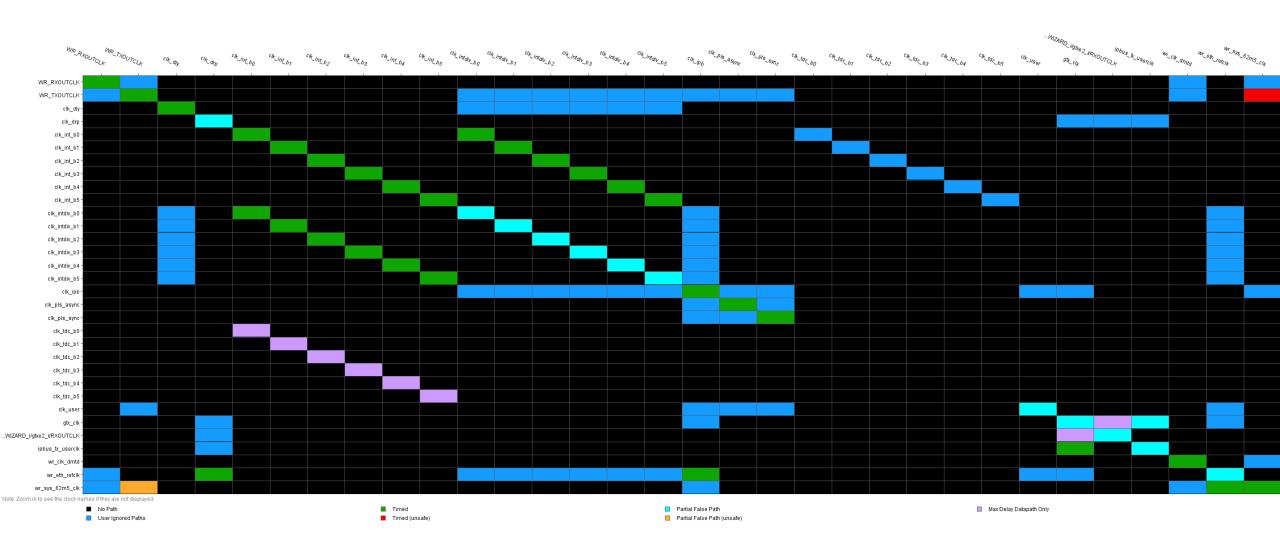

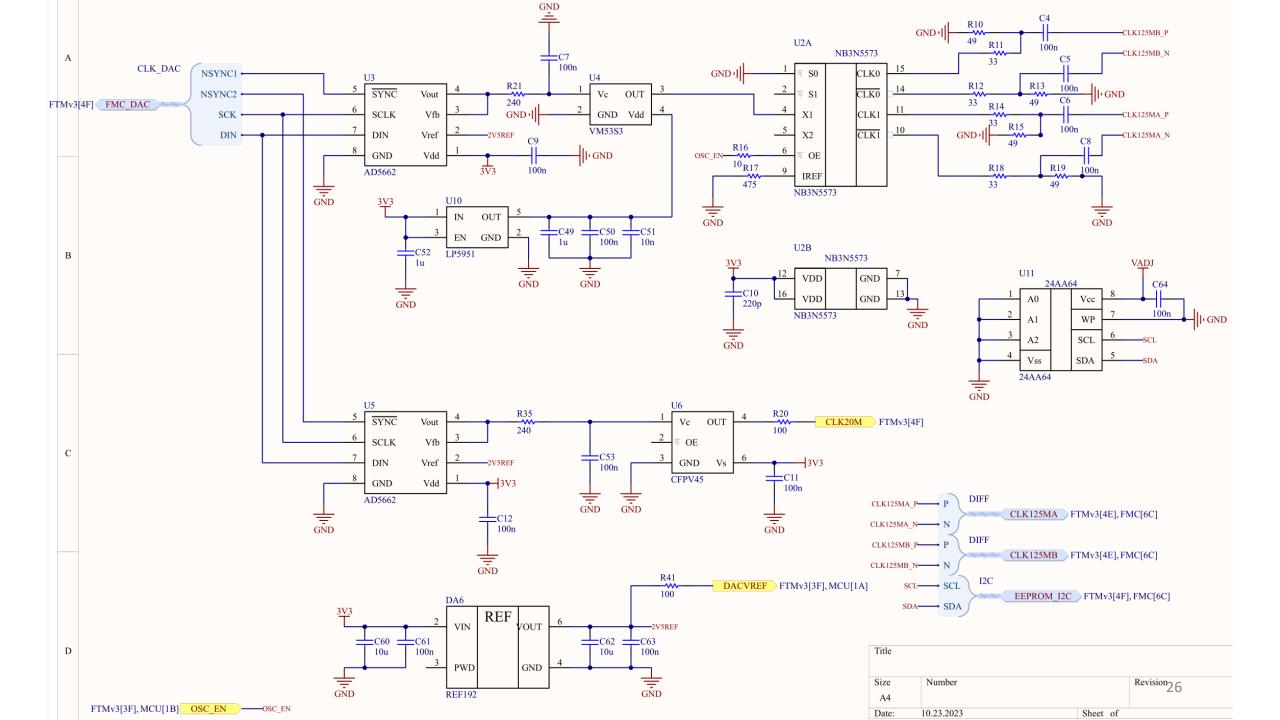

### FPGA TDC and calibration pulser clocks layout

# Master FPGA clock interaction

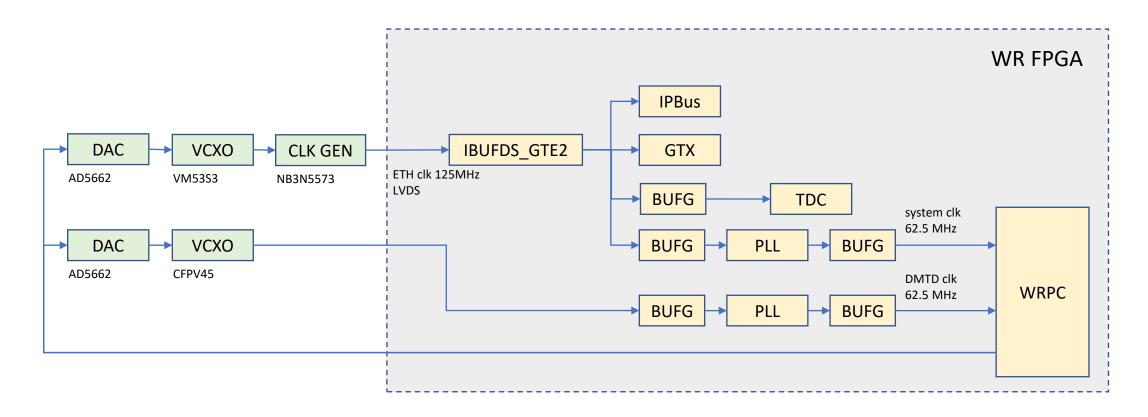

# The White Rabbit implementation

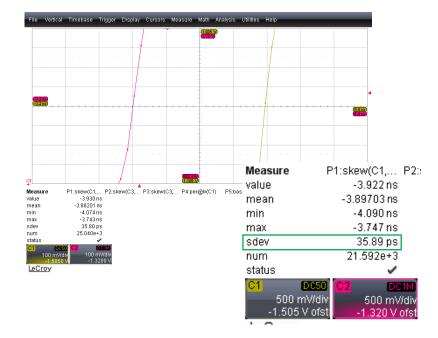

### HGND readout proto\_v2 WR tests at JINR (16 – 17 of April)

HGND readout proto v2 connected to WR master at JINR

#

orange – WR master; pink – WR slave (hgnd)

WR TX clocks 62.5 MHz:

### Clock sync jitter ~35ps (measure on FPGA output buffers)

### WR tests at JINR conclusions:

- WR synchronization works

- Tx timestamp error (reason found: generic fifo synthesis bug)

- EEPROM not works (fixed I2C wires swapped)

### Next steps June - July:

- WR error fix + project modification (mmcm replacement with pll)

- Combining WR + Ipbus + TDC FPGA modules

- 33 channels TDC tests

- Next round of WR tests at JINR

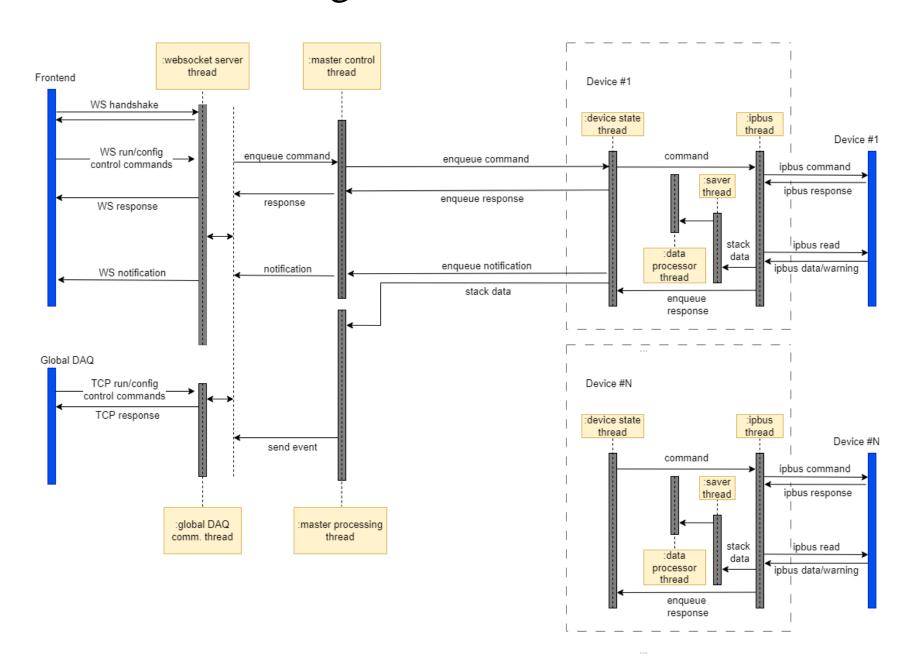

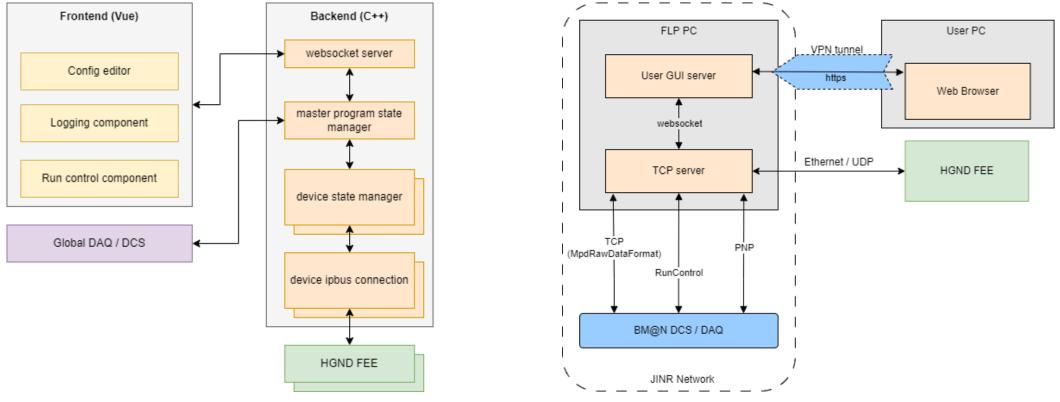

# The threading scheme of a C++ backend

# The topology of the DCS & readout software

- The detector control system consists of 2 independent modules: frontend and backend

- The backend is a C++ server running on a DCS computer in the same network with detectors.

- The server part provides write/read operations to the detectors via an IPBus connection to the control and data acquisition board.

- Frontend is the user interface for this backend. It can be implemented in various ways; the key parameters are reactivity and an ability to establish a connection via websocket with the server part.

- The current version is the Vue web application (open-source JavaScript framework).

- The interface can be run either on the DCS computer or on the operator's computer, provided that the port is available.