# **NICA\_GBT Series ASICs Development**

On behalf of the NICA\_GBT family group,

July 23th, 2024

1. Background of GBT-Series ASICs

2. NICA\_GBT Development

3. NICA\_LD/NICA\_TIA/Optical Module Development

4. Summary

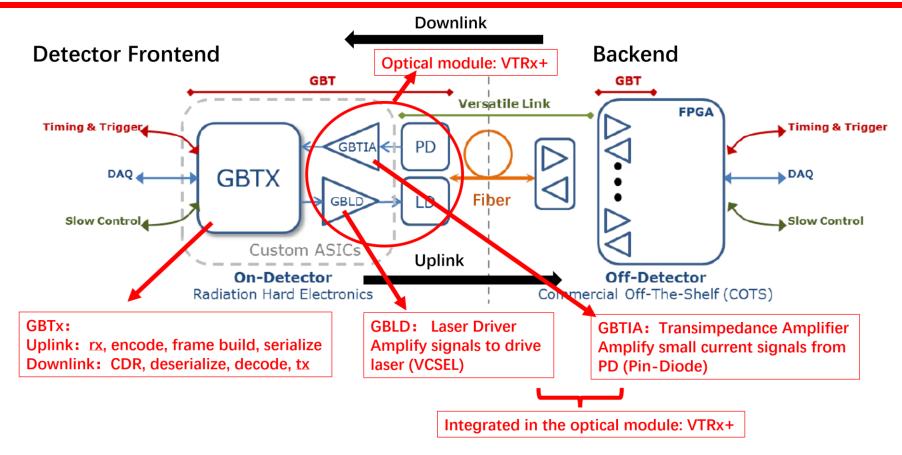

### **GBT Series ASICs Developed by CERN**

- GBT : GigBit Transceiver

- GBT Project: aims to build a high-speed, bi-directional optical data transmission system between the detector front-end and the back-end. The GBT architecture is started by CERN from 2007

- GBT Series ASICs: GBTx, GBLD, GBTIA

#### **GBT Series ASICs by CERN**

The first generation GBT ASICs by CERN were based on 130nm CMOS technology, 2011

• GBTx: uplink 5.12 Gbps, downlink 2.56 Gbps

GBLD: 5.12 Gbps/chGBTIA: 2.56 Gbps/ch

VTRx: 1Tx + 1Rx optical module (single-channel form)

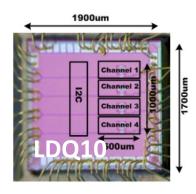

The second generation GBT ASICs by CERN were based on 65nm CMOS technology, 2019

• lpGBTx: uplink 10.24/5.12 Gbps, downlink 2.56 Gbps

GBLD: 10.24 Gbps/ch x 4 ch (array form, this chip is also called LDQ10)

• lpGBTIA: 2.56 Gbps/ch

VTRx+: 4Tx + 1Rx optical module (array form)

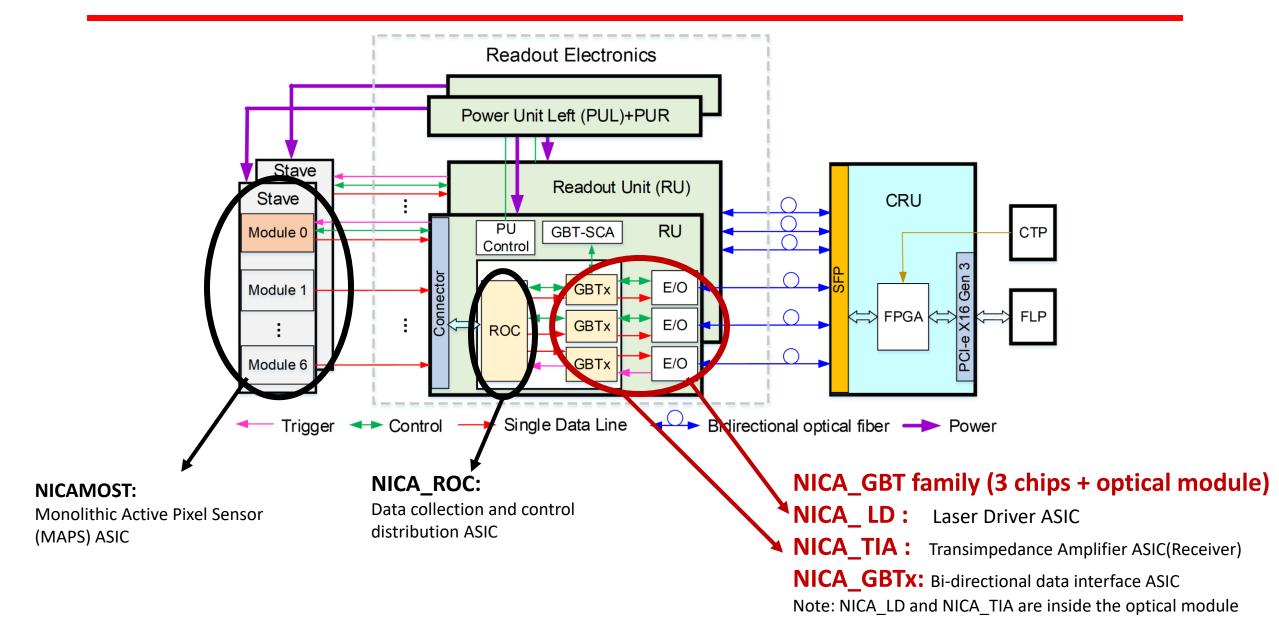

### NICA\_GBT ASICs in the Readout Electronics System

1. Background of GBT-Series ASICs

2. NICA\_GBT Development

3. NICA\_LD/NICA\_TIA/Optical Module Development

4. Summary

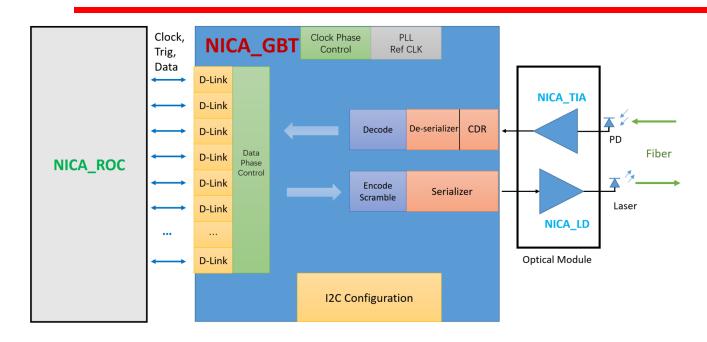

### **NICA\_GBT ASIC Development**

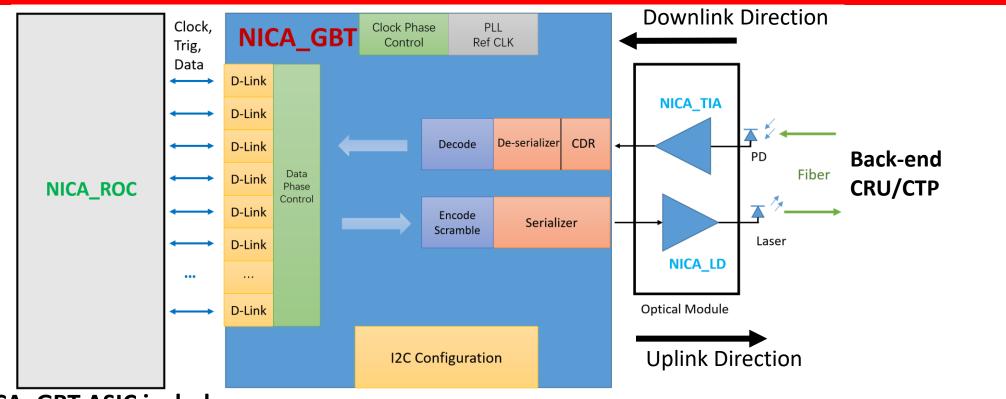

#### NICA\_GBT ASIC includes:

- High-speed Serializer 16:1 10.24 Gbps

- High-speed Deserializer 1:16 2.56 Gbps

- PLL (Phase-Lock-Loop)

5.12 GHz generate precise clock

- CDR (Clock Data Recovery) 2.56 Gbps recover clock from high-speed serial data

- Encode, Decode (Digital part)

- High-speed Tx/Rx

- Data Phase Control (Phase Aligner)

- Clock Phase control

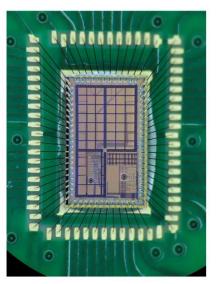

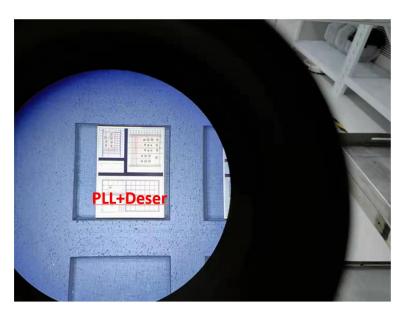

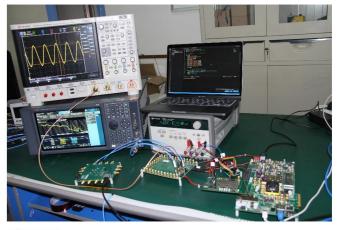

Firstly designed and tested the 5.12 GHz PLL module and the Deserializer module in 2021 (the first design related to NICA\_GBT)

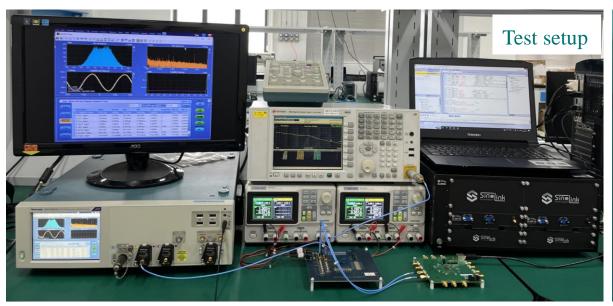

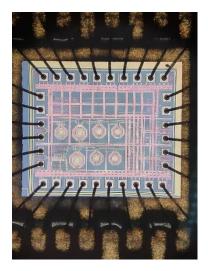

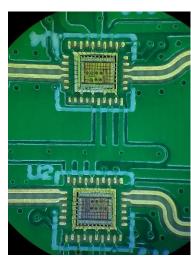

PLL + Deserializer ASIC after wire-bonding

PLL + Deserializer ASIC after wire-bonding on the test board

PLL + Deserializer ASIC practical picture under the microscope

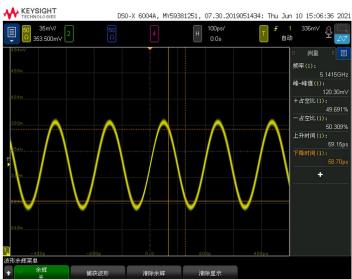

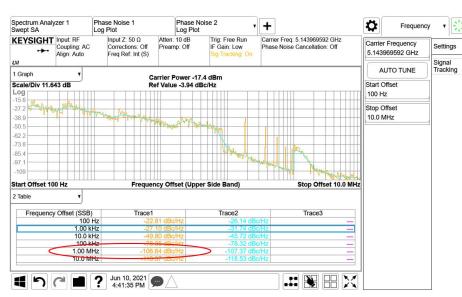

PLL locks at the targeted frequency with an adjustable range, and the tested phase noise is -106.6 dBc/Hz @1Mhz

PLL output clock in a real-time scope

PLL output clock noise analysis

Successfully verified the function of the PLL and Deseiralizer Module in NICA\_GBT ASIC

Published by IOP Publishing for Sissa Medialab

RECEIVED: November 26, 2021 Accepted: July 19, 2022 Published: September 6, 2022

12<sup>TH</sup> International Conference on Position Sensitive Detectors

12-17 SEPTEMBER, 2021

Birmingham, U.K.

PLL in NICA\_GBTx

JINST 2022

# A low noise 5.12 GHz PLL ASIC in 55 nm for NICA multi purpose detector project

C. Zhao, $^a$  D. Guo, $^{a,*}$  Q. Chen, $^a$  Z. Guo, $^a$  R. Arteche, $^b$ , $^c$  C. Ceballos, $^b$  N. Fang, $^a$  Y. Gan, $^a$  Y. Murin, $^b$  L. Yi $^a$  and X. Sun $^a$  for the MPD ITS collaboration

Published by IOP Publishing for Sissa Medialab

RECEIVED: *November 26, 2021*Accepted: *July 19, 2022*Published: *August 30, 2022*

12<sup>TH</sup> INTERNATIONAL CONFERENCE ON POSITION SENSITIVE DETECTORS

12-17 SEPTEMBER, 2021

Birmingham, U.K.

**Deserializer in NICA\_GBTx**

JINST 2022

# A 13 Gbps 1:16 deserializer ASIC for NICA multi purpose detector project

Q. Chen, $^a$  D. Guo, $^{a,*}$  C. Zhao, $^a$  Z. Guo, $^a$  R. Arteche, $^b$ , $^c$  C. Ceballos, $^b$  N. Fang, $^a$  Y. Gan, $^a$  Y. Murin, $^b$  L. Yi $^a$  and X. Sun $^a$  for the MPD ITS collaboration

• The PLL and Deserializer work has been published on behalf of the MPD ITS collaboration in JINST 2022.

<sup>&</sup>lt;sup>a</sup>PLAC, Key Laboratory of Quark and Lepton Physics (MOE), Central China Normal University, Wuhan, Hubei 430079, China

<sup>&</sup>lt;sup>b</sup>Joint Institute for Nuclear Research, Dubna, Russia

<sup>&</sup>lt;sup>c</sup> Center for Technological Applications and Nuclear Development, Havana, Cuba

<sup>&</sup>lt;sup>a</sup>PLAC, Key Laboratory of Quark and Lepton Physics (MOE), Central China Normal University, Wuhan, Hubei 430079, China

<sup>&</sup>lt;sup>b</sup>Joint Institute for Nuclear Research, Dubna, Russia

<sup>&</sup>lt;sup>c</sup> Center for Technological Applications and Nuclear Development, Havana, Cuba

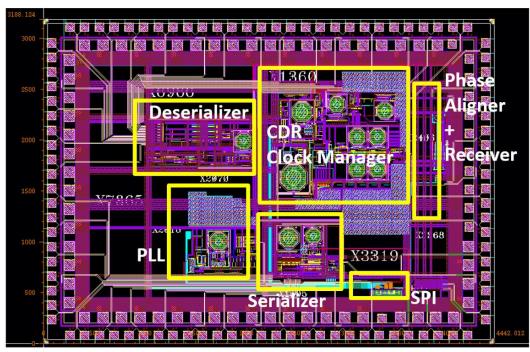

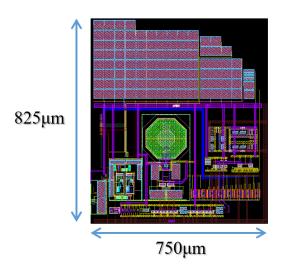

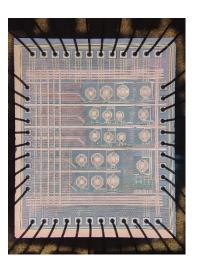

NICA\_GBT\_v1 overall layout

NICA GBT v1 includes the following sub-modules:

- 5.12Gbps/10.24 Gbps 16:1 Serializer

- 2.56Gbps/10.24 Gbps 1:16 <u>Deserializer</u>

- 2.56 Gbps/10.24 Gbps CDR

- 5.12 GHz PLL

- Clock manager module

- 160M/320M/640M/1.28Gbps Phase Aligner

- Up to 1.28 Gbps rail-to-rail Receiver(to front-end)

- 10.24 Gbps three-tap pre-emphasis

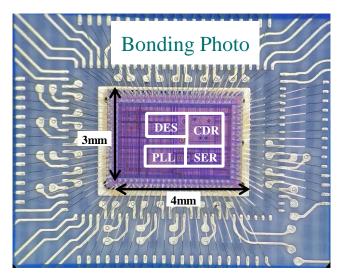

NICA\_GBT\_v1: the first prototype version of NICA\_GBT with core analog sub-modules.

Total pins: 166

Die size: 3333 um x 4444 um

(Dimensions shown in the picture will shrink

to 90%)

- Dual-row wire-bonding pads used in this version for test, and will be replaced by BGA package in the next run.

- This ASIC submitted on October 16<sup>th</sup> 2022, tested in 2023.

Process: 55nm CMOS Technology

• Chip Size: 3 mm × 4 mm

CDR core size:  $1000\mu m \times 700\mu m$

CDR power consumption:200 mW

including Rx and CML driver

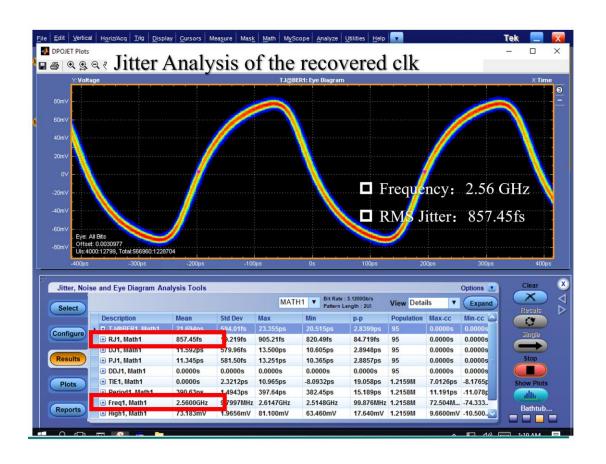

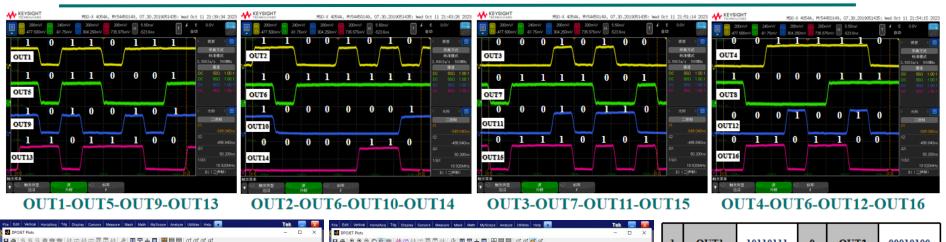

• 2.56 Gbps Clock-Data-Recovery (CDR) function was tested and verified. ∨

2.56 Gbps CDR Test Verified √

2.56 Gbps 1: 16 Deserializer + CDR were tested and verified. √

Deserializer

+

CDR Test

Verified V

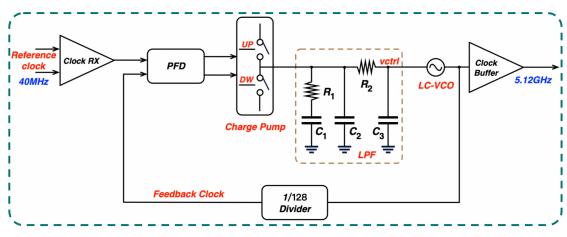

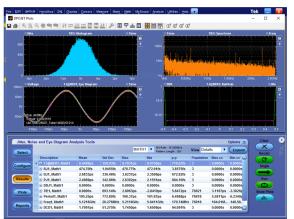

#### **PLL Structure**

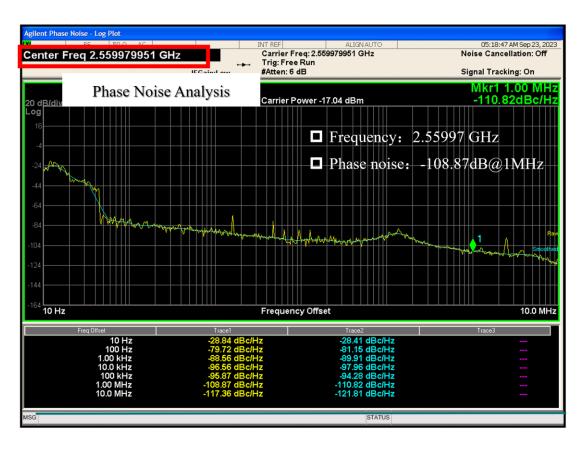

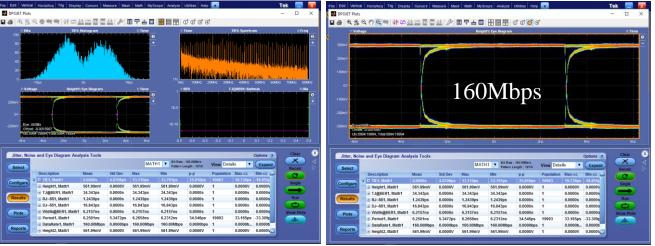

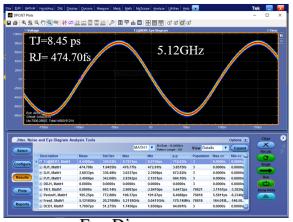

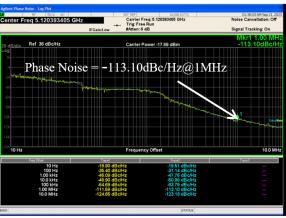

5.12 GHz PLL Test Verified √

Jitter analysis

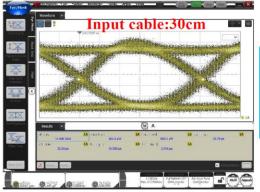

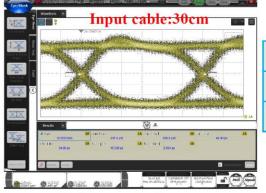

Eye Diagram

Phase Noise Curve

√ Frequency: 5.12 GHz

√ Total Jitter: 8.45ps

**✓** RMS Jitter: 474.70 fs

✓ Phase noise: -113dB@1MHz

Improve the PLL design (2021), get better performance

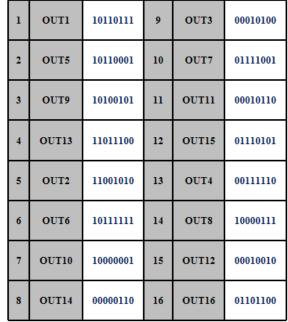

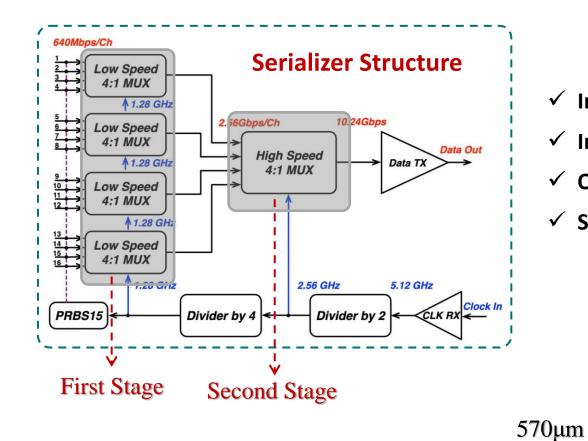

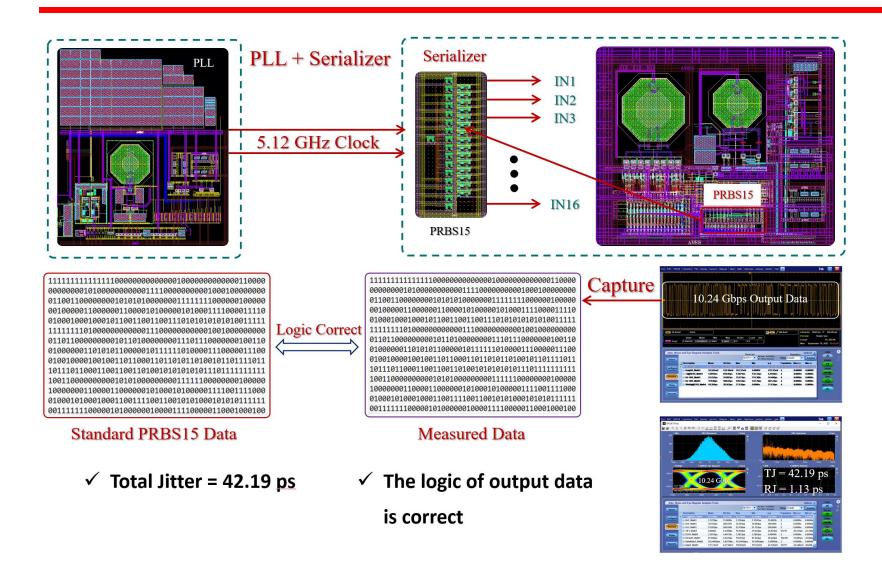

✓ First Stage: 16→4

✓ Second Stage: 4→1

✓ PRBS15: Self-test module

✓ Input Data: 640 Mbps/Ch × 16

✓ Input Clock: 5.12 GHz

✓ Output Data: 10.24 Gbps

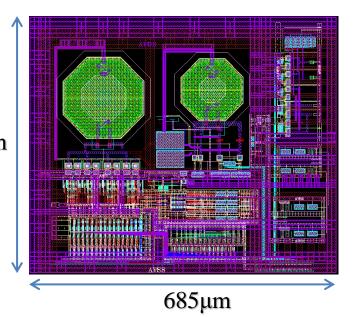

✓ Serializer core size: 685μm × 570μm

16:1 10.24Gbps Serializer Design

PLL+

Serializer Test

Verified V

### Summary about NICA\_GBT ASIC Development

#### NICA\_GBT ASIC includes:

- High-speed Serializer

- High-speed Deserializer

- PLL (Phase-Lock-Loop)

- CDR (Clock Data Recovery)

- Encode, Decode (Digital part)

- High-speed Tx/Rx

- Data Phase Control (Phase Aligner)

- Clock Phase control

Done **V**

Done √

Done √

Done √

under design (first version will be submitted within 2024)

Done √ (function verified, need to be replicated in each ch)

Designed and under testing (need to be replicated after verification)

To be designed (first version will be submitted within 2024)

1. Background of GBT-Series ASICs

2. NICA\_GBT Development

3. NICA\_LD/NICA\_TIA/Optical Module Development

4. Summary

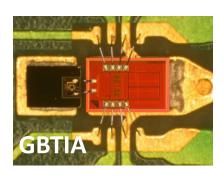

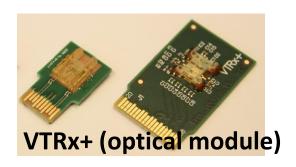

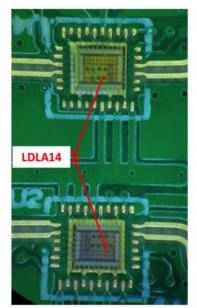

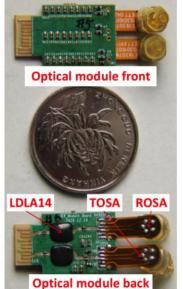

#### NICA\_LD and NICA\_TIA ASICs Development

- Two ASICs have been designed and tested in 2021~2022.

- **NICA LDLA:**

- 10 Gbps single-channel Laser Driver (Tx) + TIA +LA (Rx)

--corresponding to the VTRx(1Tx, 1Rx) single-channel form

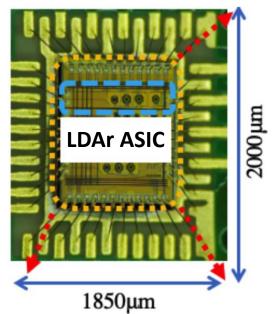

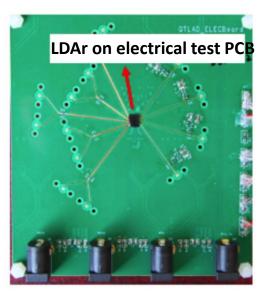

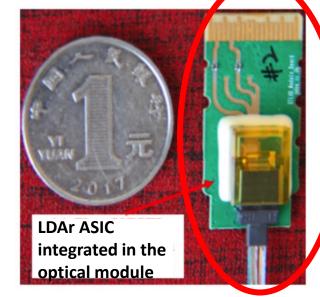

- **NICA LDAr:**

- 10 Gbps/ch Laser driver array(multi-channel Tx)

--corresponding to the VTRx+(3Tx, 1Rx) array form

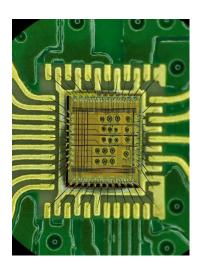

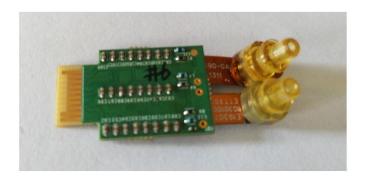

LDLA Chip

LDLA Chip on the board

LDAr Chip

LDAr Chip on the board 20

#### **LDLA ASIC Test**

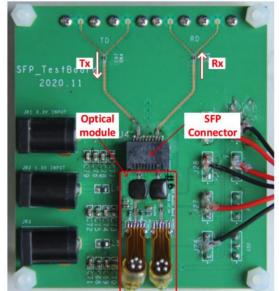

**Optical test board for LDLA chip**

LDLA chip drives TOSA to emit optical signal (Tx direction) receives small signal from ROSA (Rx direction)

- LDLA ASIC was integrated into a customized optical module based on TOSA/ROSA. (similar to VTRx)

- However we will not use this TOSA/ROSA based optical module. The optical module shown here is only for the test of the ASIC.

#### **LDLA ASIC Test**

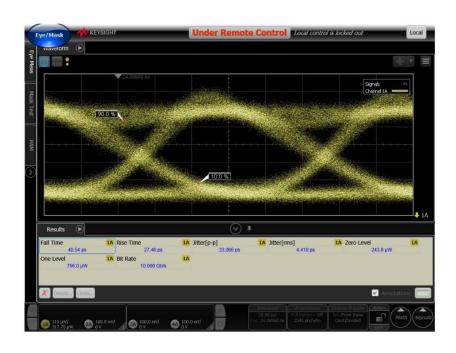

10 Gbps optical eye diagram of laser driver (Tx direction)

10 Gbps electrical eye diagram of TIA + Limiting Amplifier (Rx direction)

- 10 Gbps eyes have all passed the eye mask test.

- Tx + Rx loop back BER (bit error) test has also been conducted, BER better than 1E-12 has been achieved.

#### **LDLA ASIC Test**

The LDLA ASIC work has been published on behalf of the MPD ITS collaboration in JINST 2022.

Published by IOP Publishing for Sissa Medialab

RECEIVED: September 29, 2021 ACCEPTED: November 24, 2021 Published: January 7, 2022

22<sup>ND</sup> International Workshop on Radiation Imaging Detectors

JUNE 27-JULY 1, 2021 GHENT, BELGIUM

NICA\_LD+TIA\_v1

JINST 2022

# LDLA14: a 14 Gbps optical transceiver ASIC in 55 nm for NICA multi purpose detector project

Q. Chen, D. Guo, a,\* C. Zhao, R. Arteche, C. Ceballos, N. Fang, Y. Gan, Z. Guo, Y. Murin, X. Suna,\* and L. Yia,\* for the MPD ITS collaboration

<sup>a</sup>PLAC, Key Laboratory of Quark and Lepton Physics (MOE), Central China Normal University, Wuhan, Hubei 430079, China

<sup>b</sup> Joint Institute for Nuclear Research, Joliot-Curie st. 6, Dubna, Russia

<sup>c</sup>Center for Technological Applications and Nuclear Development, No.460 between Amargura and Teniente Rey, Havana, Cuba

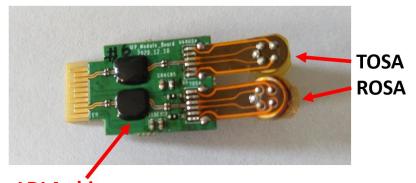

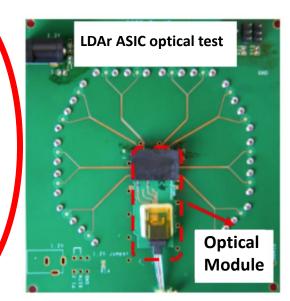

#### **LDAr ASIC Test**

- Customized array optical module (similar to VTRx+)

- This will be targeted optical module form. However, what is shown here is not the final version.

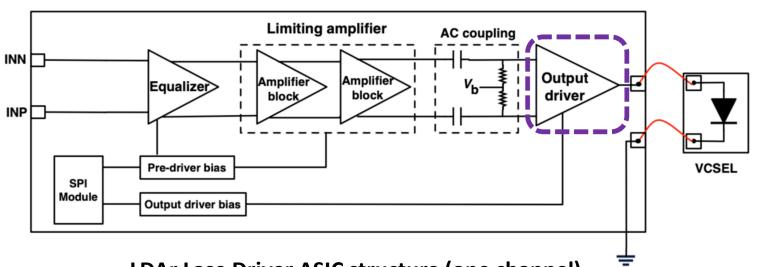

**LDAr Lase Driver ASIC structure (one channel)**

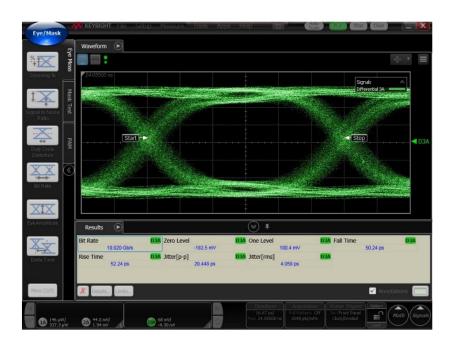

#### **LDAr ASIC Test**

| Bit Rate  | 14Gbps | RMSJ | 2.6ps   |

|-----------|--------|------|---------|

| Rise Time | 32.2ps | PPJ  | 16.6ps  |

| Fall Time | 43.8ps | Amp  | 594.2μW |

| 4 Gbps optical eye | ◆ 两种速率下眼图张开且清晰 |

|--------------------|----------------|

|--------------------|----------------|

| Bit Rate  | 10Gbps | RMSJ | 2.6ps   |

|-----------|--------|------|---------|

| Rise Time | 34.0ps | PPJ  | 15.3ps  |

| Fall Time | 48.9ps | Amp  | 589.4μW |

10 Gbps optical eye

Clear and wide-open 10 Gbps optical eye has been captured in the LDAr ASIC optical test.

Published by IOP Publishing for Sissa Medialab

RECEIVED: November 26, 2022 ACCEPTED: July 19, 2022 Published: August 23, 2022

12<sup>TH</sup> International Conference on Position Sensitive Detectors

12-17 SEPTEMBER, 2021

BIRMINGHAM, U.K.

**NICA LDAr** JINST 2022

#### A 14 Gbps VCSEL driving ASIC in 55 nm for NICA multi purpose detector project

C. Zhao, Q. Chen, Z. Guo, R. Arteche, C. Ceballos, N. Fang, Y. Gan, Y. Murin, L. Yi. D. Guo<sup>a,\*</sup> and X. Sun<sup>a,\*</sup> for the MPD ITS collaboration

<sup>a</sup>PLAC, Key Laboratory of Quark and Lepton Physics (MOE), Central China Normal University, Wuhan, Hubei 430079, China

Dubna, Russia

LDAr ASIC work has been published on behalf of the MPD ITS collaboration in JINST 2022.

<sup>&</sup>lt;sup>b</sup>Joint Institute for Nuclear Research,

<sup>&</sup>lt;sup>c</sup>Center for Technological Applications and Nuclear Development, Havana, Cuba

1. Background of GBT-Series ASICs

2. NICA\_GBT Development

3. NICA\_LD/NICA\_TIA/Optical Module Development

4. Summary

#### NICA\_GBT ASIC

#### NICA\_GBT ASIC includes:

High-speed Serializer

High-speed Deserializer

PLL (Phase-Lock-Loop)

CDR (Clock Data Recovery)

Encode, Decode (Digital part)

Done √

under design (first version will be submitted within 2024)

• High-speed Tx/Rx Done √ (function verified, need to be replicated in each ch)

Data Phase Control (Phase Aligner)

Designed and under testing (need to be replicated after verification)

Clock Phase control

To be designed (first version will be submitted within 2024)

#### What else needs to be done:

- Encode, Decode (Digital part) design, test and iterative design if needed

- Phase Aligner test, iterative design(if needed) and integration

- Clock Phase control design, test and integration

- Overall ASIC integration (Large-scale anlog-digital-mixed ASIC)

The above work are planned to be achieved in 2025~2026

- BGA package (design, manufacture, test)

- Chip test (BGA)

#### NICA\_LD, NICA\_TIA ASICs and optical module

- NICA\_LD

- Core design has been tested and verified

Done V

- What else needs to be done?

- Optimize the design (chip area and the power consumption)

- The final version integration (full four-channel form)

- NICA\_TIA

- Core design has been tested and verified

Done V

- What else needs to be done?

- Optimize the design (data rate and the power consumption)

- The final version design

- Optical module

- Prototype has been designed and tested

Done V

- What else needs to be done?

- Optimize the design (related to stable and reliable mechanics, assembly ..)

- The final version.

All the NICA\_LD, NICA\_TIA and optical module work is planned to be done in 2025.

# Thanks!