Neutron Radiation Effects on the Reliability of the Cyclone V FPGA Development Board 62nd meeting of the PAC for Particle Physics

Youmna Ghoneim <sup>a,c\*</sup>, Sergey Movchan <sup>a</sup>, Ilya Chepurchenko <sup>a</sup>, Rafael Isayev <sup>a,b</sup>, Kirill Mikhailov <sup>a</sup>, konstantin Udovichenko <sup>a</sup>

a) Joint Institute for Nuclear Research, 6 Joliot-Curie St., 141980 Dubna, Russia.

b) Innovation and Digital Development Agency, Baku, Azerbaijan.

c) National Research Tomsk Polytechnic University, 634050, Tomsk Russia.

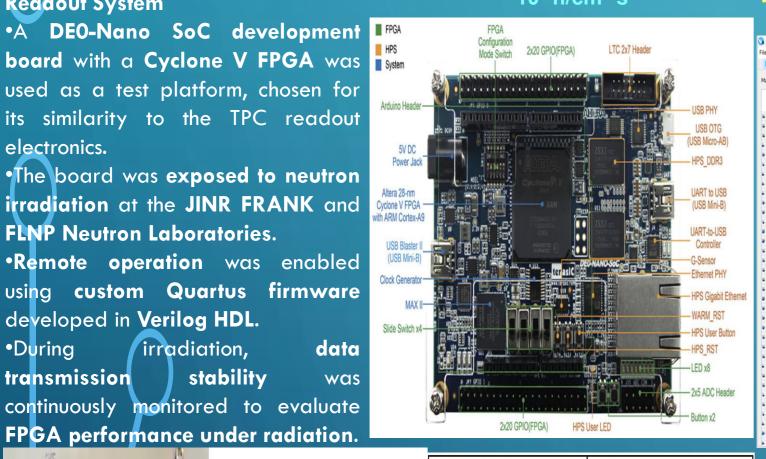

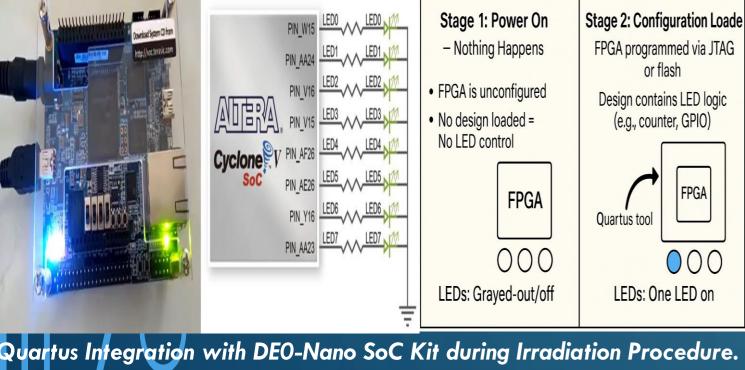

Agenda Item: Radiation Testing of Cyclone V FPGA Using DEO-Nano **SoC Development Board.**

**Objective:** Evaluate the performance and stability of Cyclone V FPGA under neutron irradiation, as used in the Time Projection Chamber (TPC) of the Multi-Purpose Detector (MPD).

Test Platform: DEO-Nano SoC Development Board, controlled via Verilogbased QUARTUS firmware.

Irradiation Site: JINR FRANK and Neutron Laboratories, Use of shielding materials to protect components except the FPGA.

Key Focus Areas on DEO-Nano SoC Development Board.

- Data transmission stability and firmware efficiency under radiation.

- Impact of radiation on power modules and ARM processor performance.

## **Radiation Analysis:**

- Assessment of FPGA logic errors and power reliability postirradiation.

- Fluence estimation using silicon sensors measuring leakage current due to irradiation damage.

## Introduction

## **TPC Overview**

The Time Projection Chamber (TPC) is the main tracking detector in the established via USB Blaster and JTAG. Multi-Purpose Detector (MPD) at the NICA collider.

t tracks charged particles produced in nucleus-nucleus collisions, providing Quartus software served as both a remote-control and precise spatial and momentum information.

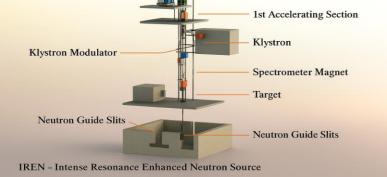

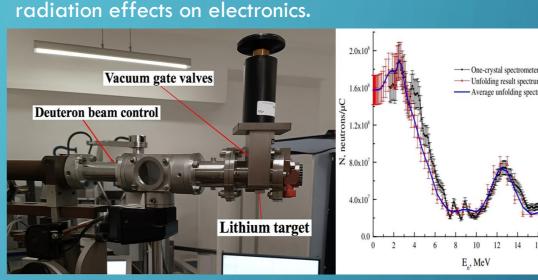

- Irradiation Process for the Electronic Kit Utilizing the IREN Accelerator <u>IREN (Intense Resonance Neutron Source)</u>

- •Located at JINR, IREN is a pulsed neutron facility.

Designed to produce high-intensity neutron bursts through nuclear reactions. •Supports research in nuclear physics, neutron spectroscopy, and materials science.

# **Neutron-Producing Target**

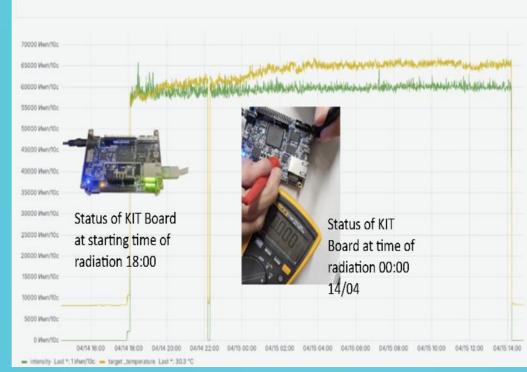

Neutron flux intensity indicators over the irradiation period for the Deo Nano SoC KIT board "Имп /10с" -"Imp/10s" (Impulses per 10 seconds).

Results from irradiating the Cyclone V FPGA on the DEO-Nano SoC Kit using the IREN accelerator.

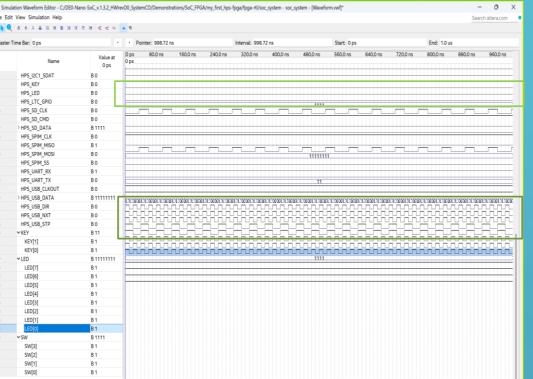

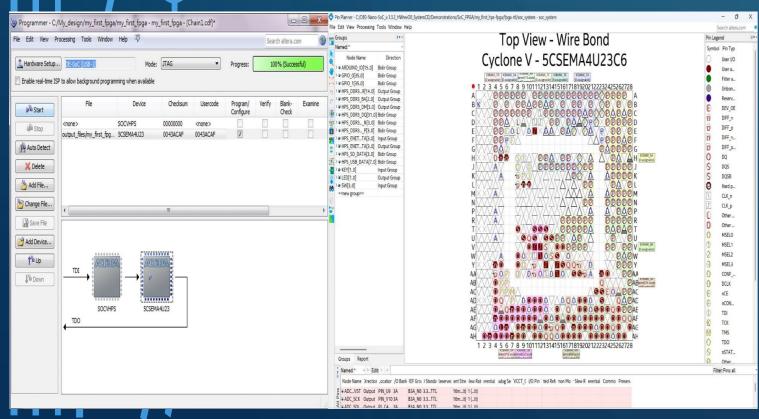

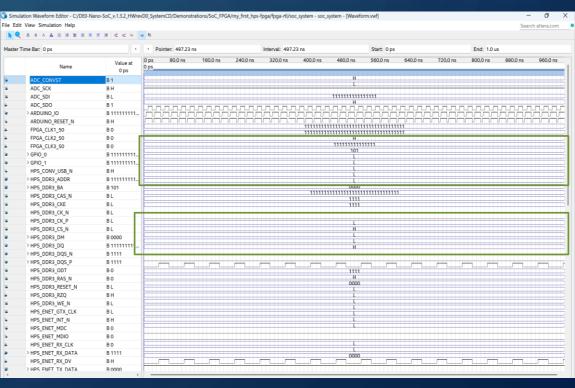

The DEO-Nano SoC kit's functionality was validated using Verilog, with PC-to-FPGA communication

simulation tool using Verilog code from earlier tests.

Results show that irradiation from the IREN Accelerator disrupted the DEO-Nano SoC kit's power system, damaging memory, ports, Ethernet, and power delivery.

Ethernet port, (b) UART to USB interface, and (c) HPS DDR3

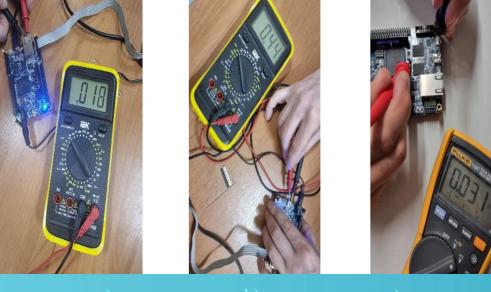

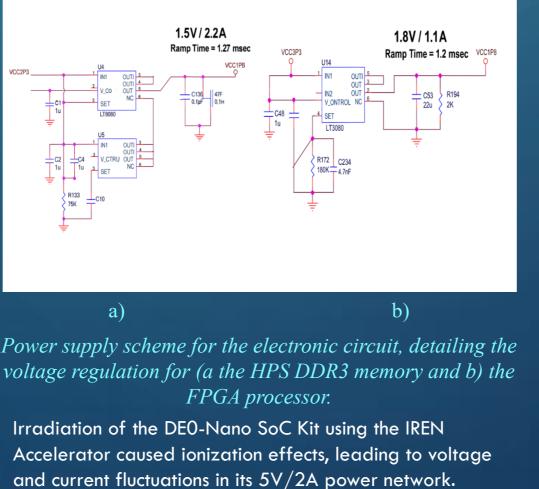

a) Radiation-induced disruption in power delivery to the FPGA: instability in the +1.2 V supply to the processor due to irradiation effects on voltage regulation, (b) damaged external 5V/2A power supply, and (c) its power input connection of 5V.

Irradiation Setup for the DEO-Nano SoC Kit Using the EG-5 Accelerator

## **Radiation Exposure Setup at JINR**

eutron irradiation was carried out at the Neutron

The kit board temporarily stop functioning and then resume during irradiation due to radiation-induced transient faults, such as Single Event Upsets (SEUs) or Single Event Functional Interrupts (SEFIs). These effects can momentarily disrupt the FPGA's operation without causing permanent damage.

# **Experimental Results**

|                                                          |                | 30<br>30<br>30<br>10<br>10                                                                                 |  |  |

|----------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------|--|--|

| -FPGA LED                                                | HPS LED        |                                                                                                            |  |  |

| Radiation disrup<br>regulators and b<br>causing instabil | ower circuits, | <ul> <li>Shut down Recovery</li> <li>Each shuth down followed by a 30-minute automatic recovery</li> </ul> |  |  |

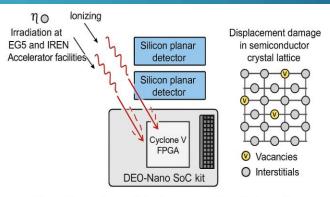

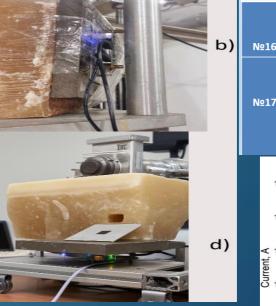

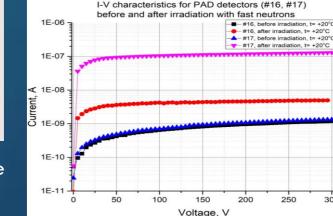

**Determining Fast Neutron Fluence Using Planar Silicon Detectors**

Two sillcon planar detectors were placed above the Cyclone V FPGA during irradiation at ad IDEN Accolorator facilitie

t neutron

ing its

## •Cylindrical TNF target: 40 mm (diameter) $\times$ 100 mm (height) •Enclosed in a 160 mm diameter aluminum tank.

#### **Neutron Production Mechanism**

•Target material: Tungsten-based alloy (VNZh-90) with non-multiplying properties •Reaction type: A W ( $\gamma$ , n) A–1 (neutron emission from tungsten isotopes)

Two-step neutron generation process: 1. High-energy electrons produce bremsstrahlung gamma rays upon hitting the target

2.Gamma rays interact with tungsten nuclei, generating neutrons via  $(\gamma, n)$ reactions

Radiation Testing of FPGA-Based

Methodological

**FLNP** Neutron Laboratories.

developed in Verilog HDL.

irradiation,

stability

Readout System

electronics.

•During

transmission

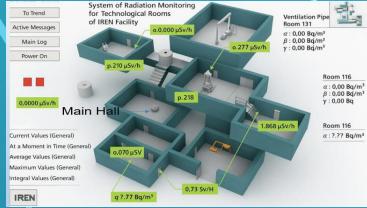

Dosimetry screen showing radiation levels after the exposure period ended for the KIT board, taken in the main hall and technical rooms of the IREN Facility, with the primary irradiation unit powered off.

Broad neutron energy range: thermal to fast neutrons •Fast neutron energy: **20–30 MeV**  During KIT board irradiation: flux was ~10<sup>7</sup> n/cm<sup>2</sup>·s

### Results from irradiating the Cyclone V FPGA on the DEO-Nano SoC Kit using the IREN accelerator.

| ation Waveform Editor - C:/DE0-N | lano-SoC_v.1.3.2_HWrev | vD0_Syster   | nCD/Demonstr   | ations/SoC_FPG | A/my_first_hps- | fpga/fpga-rtl/so | c_system - soc_s | ystem - [Wavefo | orm.vwf]*                               |          |          |            | -        | - 0 )          |

|----------------------------------|------------------------|--------------|----------------|----------------|-----------------|------------------|------------------|-----------------|-----------------------------------------|----------|----------|------------|----------|----------------|

| View Simulation Help             |                        |              |                |                |                 |                  |                  |                 |                                         |          |          |            | Sear     | rch altera.com |

| A & A & X X X X X X              | 建油 电电压                 | 4 5          |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| Time Bar: 0 ps                   | •                      | • Poi        | nter: 760.77 n | \$             |                 | Interval: 760.7  | 17 ns            |                 | Start: 0 ps                             |          |          | End: 1.0 u | 5        |                |

| Name                             | Value at<br>0 ps       | 0 ps<br>0 ps | 80.0 ns        | 160.0 ns       | 240.0 ns        | 320.0 ns         | 400.0 ns         | 480.0 ns        | 560.0 ns                                | 640.0 ns | 720.0 ns | 800.0 ns   | 880.0 ns | 960.0 ns       |

| ADC_CONVST                       | B 1                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| ADC_SCK                          | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| ADC_SDI                          | BO                     |              |                |                |                 |                  |                  | 11111111111     | 11111                                   |          |          |            |          |                |

| ADC_SDO                          | B 1                    |              |                |                |                 |                  |                  |                 |                                         |          | www      |            |          |                |

| > ARDUINO_IO                     | B 11111111             | LULL         |                |                | iiii            | йййй             | ттт              | inin            | ההנהנה                                  | תתת      | mmm      | inini      | ттт      | ттт            |

| ARDUINO_RESET_N                  | BH                     | ירירו        |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| FPGA_CLK1_50                     | B 0                    |              |                |                |                 |                  |                  |                 | 1111111111111                           |          |          |            |          |                |

| FPGA_CLK2_50                     | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| FPGA_CLK3_50                     | B 0                    |              |                |                |                 |                  |                  | 0000000000      | 00000                                   |          |          |            |          |                |

| > GPIO_0                         | B 111111111            |              |                |                |                 |                  |                  | 000             |                                         |          |          |            |          |                |

| > GPIO_1                         | B 11111111             |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_CONV_USB_N                   | 80                     |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| > HPS_DDR3_ADDR                  | B 00000000             |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| > HPS_DDR3_BA                    | B 000                  |              |                |                |                 |                  |                  | 0000            |                                         |          |          |            |          |                |

| HPS_DDR3_CAS_N                   | BO                     |              |                |                |                 |                  | 0000000          | 1111            | 000000000000000000000000000000000000000 | 0        |          |            |          |                |

| HPS_DDR3_CKE                     | BO                     |              |                |                |                 |                  |                  | 1111            |                                         |          |          |            |          |                |

| HPS_DDR3_CK_N                    | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_DDR3_CK_P                    | BO                     |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_DDR3_CS_N                    | B 0                    |              |                |                |                 |                  |                  | Ĥ               |                                         |          |          |            |          |                |

| > HPS_DDR3_DM                    | B 0000                 |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| > HPS_DDR3_DQ                    | B 00000000             |              |                |                |                 |                  |                  | н               |                                         |          |          |            |          |                |

| > HPS_DDR3_DQS_N                 | B 1111                 |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| > HPS_DDR3_DQS_P                 | B 1111                 |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_DDR3_ODT                     | BO                     |              |                |                |                 |                  |                  | 1111            |                                         |          |          |            |          |                |

| HPS_DDR3_RAS_N                   | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_DDR3_RESET_N                 | BO                     |              |                |                |                 |                  |                  | 0000            |                                         |          |          |            |          |                |

| HPS_DDR3_RZQ                     | BH                     |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_DDR3_WE_N                    | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_ENET_GTX_CLK                 | BO                     |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_ENET_INT_N                   | BH                     |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_ENET_MDC                     | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_ENET_MDIO                    | B 0                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| HPS_ENET_RX_CLK                  | B 1                    |              |                |                |                 |                  |                  |                 |                                         |          |          |            |          |                |

| > HPS_ENET_RX_DATA               | B 1111                 | -            |                |                |                 |                  |                  | 1111            |                                         |          |          |            |          |                |

| HPS_ENET_RX_DV                   | BH                     |              | -              |                |                 | ·                | L                |                 |                                         |          |          | -          | 1        |                |

| Hourse and the second and the second                                                                                                                                                    | and IREN Accelerator facilities                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physics Laboratory of the Joint Institute for Nuclear                                                                                                                                   |                                                                                                                                                                                                                   |

| Research (JINR), using neutrons generated by the EG-5<br>electrostatic accelerator.<br>•The neutron-producing reaction was: Li (d, n) <sup>8</sup> Be                                   | Silicon detectors are sensitive to fast<br>irradiation.<br>•Radiation damages silicon, increasin<br>reverse bulk (dark) current.                                                                                  |

| Irradiation Schedule<br>•April 3rd: 11:00 AM – 5:00 PM<br>•April 4th: 10:00 AM – 5:00 PM<br>Total Exposure Duration                                                                     | <ul> <li>This current increase is proportional</li> <li>Neutron fluence (Φ)</li> <li>Sensitive volume (V) of the definition Formula</li> <li>Δ I = α × Φ × V,</li> </ul>                                          |

| •Approx. 10 hours and 40 minutes total exposure<br>Estimated neutron flux: 0.5 × 10 <sup>7</sup> n/cm <sup>2</sup> ·s~30% of<br>neutrons had energies near 14 MeV, suitable for testing | <ul> <li>ΔI = I - I<sub>0</sub> (A)</li> <li>I: Post-irradiation dark current</li> <li>I<sub>0</sub>: Pre-irradiation dark current</li> <li>Both measured at full depletion v<br/>normalized to +20 °C</li> </ul> |

|                                                                                                                                                                                         |                                                                                                                                                                                                                   |

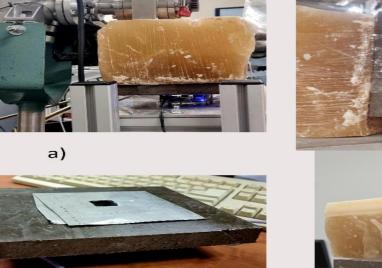

Shielding of the Deo Nano SOC KIT Board

c)

a) installation of the EG5 accelerator's third channel to expose the electronic kit board for neutron radiation source.

b) Connect the kit board for the FPGA Cyclone V to the power supply and make the connection between the kit board and the Leakage current increases more personal computer using UART to USB (USB MINI-B) Cable to remote rapidly and breakdown voltage control the kit while being irradiated.

c) two layers of Borated polyethylene and Cadmium.

|                | <ul> <li>I his current increase is proportional to:         <ul> <li>Neutron fluence (Φ)</li> <li>Sensitive volume (V) of the detector</li> </ul> </li> <li>Fluence Estimation Formula</li> </ul> |                                                                                |                                              |                                                                                                                                                                                                                   |                                 |                    |                                                |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|------------------------------------------------|--|--|--|

|                | $\Delta I = \alpha  \times  \Phi \times  V,$                                                                                                                                                      |                                                                                |                                              |                                                                                                                                                                                                                   |                                 |                    |                                                |  |  |  |

| F              | <ul> <li>∠I = I - I₀ (A)</li> <li>I: Post-irradiation dark current</li> <li>I₀: Pre-irradiation dark current</li> <li>Both measured at full depletion voltage and normalized to +20 °C</li> </ul> |                                                                                |                                              |                                                                                                                                                                                                                   |                                 |                    |                                                |  |  |  |

| ٦              | <b>Φ (cm⁻²):</b> 1                                                                                                                                                                                | MeV-equivalen                                                                  | t fast neutron                               | fluence                                                                                                                                                                                                           |                                 |                    |                                                |  |  |  |

| <u>↓</u><br>20 | α; = (5 ± 0.5)<br>• Curre<br>• For 1<br>anne<br>V = d × S (cl<br>• Sens<br>• d = d                                                                                                                | × <b>10<sup>−17</sup> A/cm</b> :<br>ent-related darr<br>MeV neutrons<br>aling) | nage constant<br>s at +20 °C (ex<br>ess (cm) | Final Fluence Calculation<br>$\Phi = \Delta I / (\alpha_i. V)$ ,<br>By measuring $\Delta I$ and knowing $\alpha_i$ , d, and S,<br>the neutron fluence $\Phi$ (n/cm <sup>2</sup> ) can be accurated<br>determined. |                                 |                    |                                                |  |  |  |

|                | Nº<br>Silicon                                                                                                                                                                                     | d, mm                                                                          | S, mm²                                       | l, n A (V =<br>100 V)<br>(before                                                                                                                                                                                  | l, n A (V =<br>100 V)<br>(after | ΔΙ, nA<br>(V = 100 | Ф <sub>п, eq</sub> <1MeV>                      |  |  |  |

|                | Detector                                                                                                                                                                                          |                                                                                |                                              |                                                                                                                                                                                                                   | irradiatio                      | V)                 | /см <sup>2</sup>                               |  |  |  |

| »)             | Nº16                                                                                                                                                                                              | 0.266                                                                          | 13                                           | n)<br>0.6                                                                                                                                                                                                         | n)<br>4.21                      | 3.56               | 2.06×10 <sup>10</sup><br>Van de Graaf          |  |  |  |

|                | Nº17                                                                                                                                                                                              | 0.251                                                                          | 13                                           | 0.7                                                                                                                                                                                                               | 105                             | 104                | 6.36×10 <sup>11</sup><br>Van de Graaf<br>+IREN |  |  |  |

|                | I-V characteristics for PAD detectors (#16, #17)<br>before and after irradiation with fast neutrons                                                                                               |                                                                                |                                              |                                                                                                                                                                                                                   |                                 |                    |                                                |  |  |  |

decreases in silicon detectors irradiated with the IREN accelerator.

Voltage readings and schematics reveal that the DEO-Nano SoC kit's power regulation circuits for the HPS DDR3 and FPGA are malfunctioning.

This disruption in power distribution likely resulted from irradiation exposure in the IREN Accelerator.

These disruptions resulted in malfunctions of key

components, including the HPS\_DDR3 memory, UART-to-

USB, USB Blaster II, and the Ethernet port (Figure a-c).

d) shielding materials consist of three layers of (Borated polyethylene, Paraffin, and Cadmium).

## Conclusion

### Impact of Radiation on Power System

- Irradiation caused consistent switching behavior, confirmed by LED activity on FPGA and HPS.

- Observations recorded using Quartus Universal energy setups. Waveform Simulator.

- Voltage regulators and power circuits became Cyclone V FPGA remained functional unstable, leading to system shutdowns every ~80 for about 80 minutes before minutes.

- The board automatically recovered after ~30 minutes each time.

- Highlights increased risk of malfunction or damage, especially without adequate FPGA shielding.

# Radiation testing on **DEO-Nano SoC** boards was conducted at the EG-5 and

- **IREN** facilities using two neutron

- •In Setup 1 (~3 MeV neutrons), the

- experiencing periodic shutdowns, each followed by a **30-minute** automatic recovery. The exact cause of the shutdowns remains under investigation.

•In Setup 2 (20-40 MeV neutrons), the board's power system failed entirely after approximately **4 hours** of exposure, indicating a severe impact at higher energy levels.

### Acknowledgement

We gratefully acknowledge Dr. Nicolay Zamyatin for his significant contributions to the investigation and experimental phases of this work. His expertise and support played a vital role in the development and completion of this study.