# Multi-channel pulse counter based on the Altera FPGA

Ilya Butorov, DLNP JINR

Alushta-2019, Alushta, 11th of June

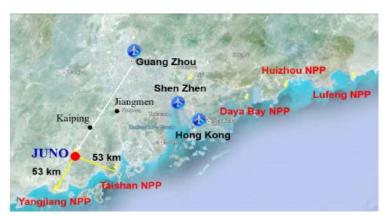

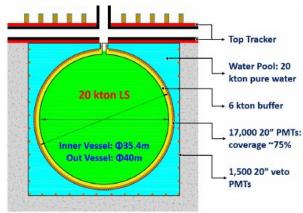

# JUNO experiment: Physics and layout

## Main goals:

- Neutrino mass hierarchy

- Precision of neutrino oscillation parameters  $\Delta m^2_{21}, \Delta m^2_{32}, \sin^2\theta_{12}$  below 1%

#### Other:

- Astroparticle physics

- SN bursts, diffuse SN neutrinos

- Solar neutrinos

- Atmospheric neutrinos

- Geoneutrino (U+Th neutrino flux)

- Indirect DM search

## Kaiping, Jiangmen, Guangdong

JUNO experiment: Detector

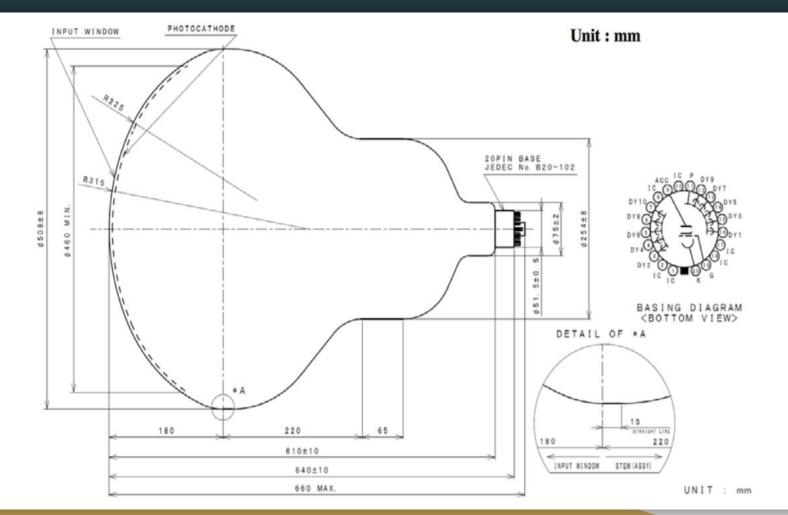

## PMTs requirements:

- High and uniform quantum efficiency

- Good SPE detector capability

- Large dynamic range

- Low noise rate

- High reliability

- Long lifetime

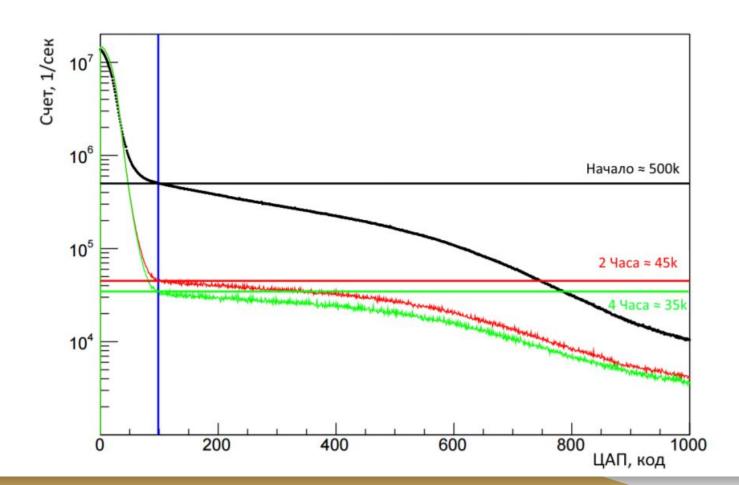

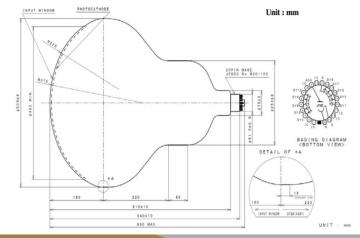

# PMT testing: Ongoing status

## ~20 000 LPMTs are being tested:

- PMT scanning station: precise measurements

- Container system:

Long-term stability tests are to be carried out

## **Control block for PMT scanning station**

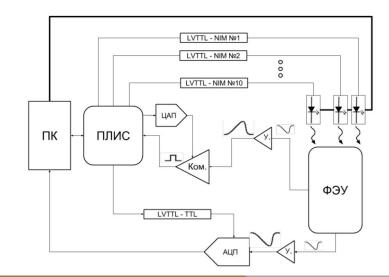

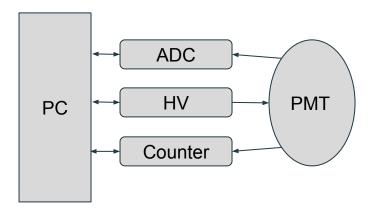

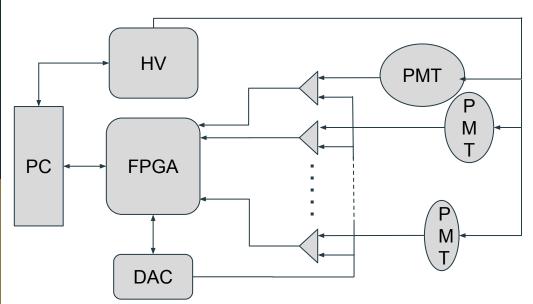

# Multi-channel counter

# Conceptual design

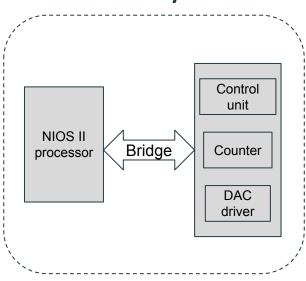

# **FPGA layout**

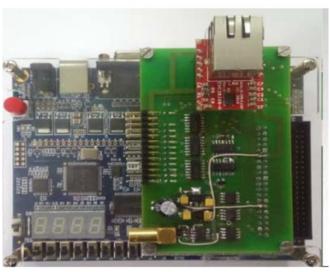

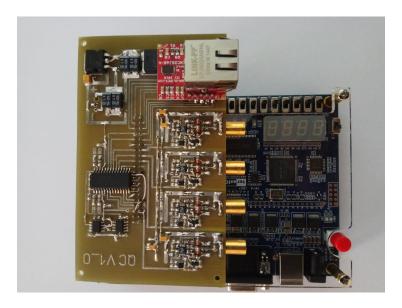

# Multi-channel counter: first prototype

#### **Inner blocks**

Control unit, counter, DAC driver Mealy machine Verilog/System Verilog HDL

## NIOS II CPU

Altera IP Core

## **Quad-channel pulse counter**

- Altera DE0 Development and Education Board

- Texas Instruments 12-Bit Quad Voltage Output DAC7624

- Linear Technology 4ns,

150MHz Dual Comparator

- Olimex ENC28J60-H Development Board

#### Software core

UDP listener over Ethernet Infinite cycle C

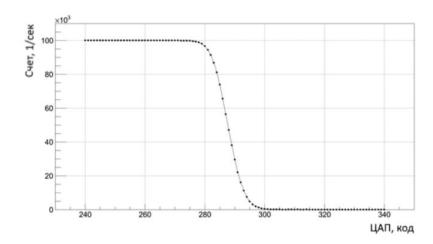

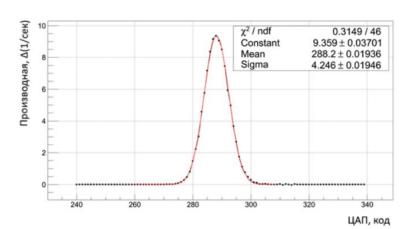

# Multi-channel counter: ongoing status

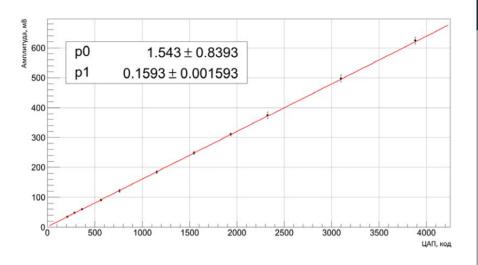

KEYSIGHT 33600A Series Waveform Generator tests:

Rectangular pulses → Missing events

$100kHz \rightarrow 999995$  counts

$1MHz \rightarrow 999956$  counts

$10MHz \rightarrow 99999547$  counts

On-board MEC oscillator:

±25ppm - ±100ppm

Aging factor

±3ppm/year (25°C)

# Multi-channel counter: status & future prospects

#### What has been done:

- DAC driver and quad-channel pulse counter (Verilog HDL)

- UDP server (C)

- Library for encoding/decoding of input and output FPGA data (C)

- Command-line user interface (C, Python)

- Scale the project for more channels (logic part of the firmware)

- Graphical user interface (Python, Tkinter) has not been finished yet

#### To be done:

- Perform channels voltage calibration

- Perform tests with true noise signals (PMT, SiPM)

- Move to another FPGA board

Thank you for your attention!