# MPD Data Acquisition System Status

#### Ilia Slepnev for the MPD & BM@N DAQ working group

A. Baskakov, S. Bazylev, V. Burtsev, A. Egorov, A. Fediunin, I. Filippov, T. Gandjelashvili, S. Kuklin, A. Shchipunov, A. Shutov, I. Slepnev, V. Slepnev, N. Tarasov, A. Terletskiy

#### Joint Institute for Nuclear Research

The third Collaboration meeting of the MPD and BM@N experiments at the NICA Facility

# Outline

- DAQ Architecture

- ► TOF, FFD electronics

- ECAL, FHCAL electronics and cooling

- Common readout unit

- DAQ Control Software

- DAQ IT Infrastructure

For more details please proceed to >>> MPD DAQ TDR

### **MPD Data Acquisition System**

#### Properties

Reliable data transfer. Pipeline operation with synch and async stages. Extensive diagnostics in hardware and software. Monitoring, logging. Data integrity check on all levels. CRC, sequence numbers, FEC. Fault tolerant, Highly available. Fast self recovery after SEU events. Distributed, scalable, extendable. Based on open and industry standards. Flexible architecture. Partitioning for independent subsystem operation.

#### **Operation Modes**

Multiple hardware trigger classes Uncompressed, full raw data during MPD commissioning Large calibration data events at low trigger rate High multiplicity events from central collisions at planned trigger rate

#### DAQ in numbers

Up to 7 kHz trigger rate, over 1 MB compressed event size to storage device From 5 to 30 GB/s uncompressed raw data rate from readout cards to FLP Approx. 200 TB in 2020 to 20 PB in 2023 annual stored data size

I.Slepnev, JINR

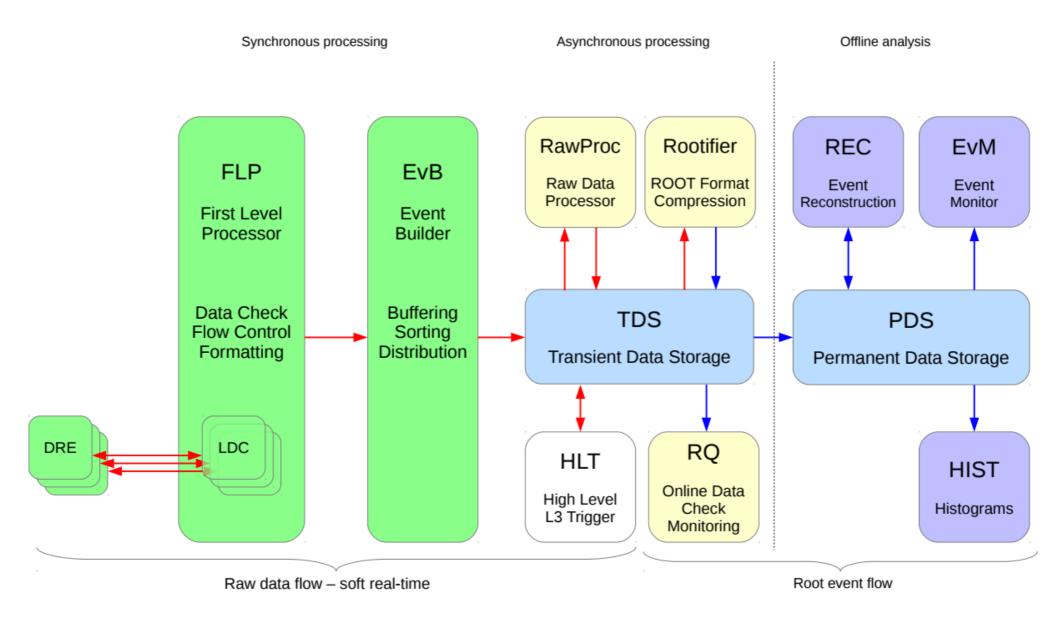

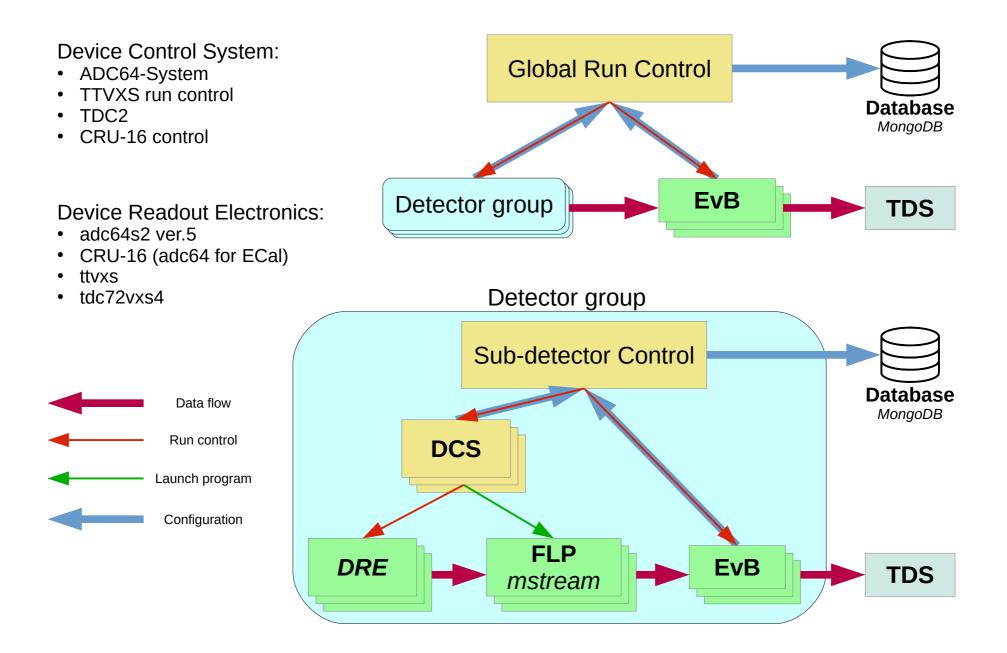

#### **MPD DAQ Architecture**

I.Slepnev, JINR

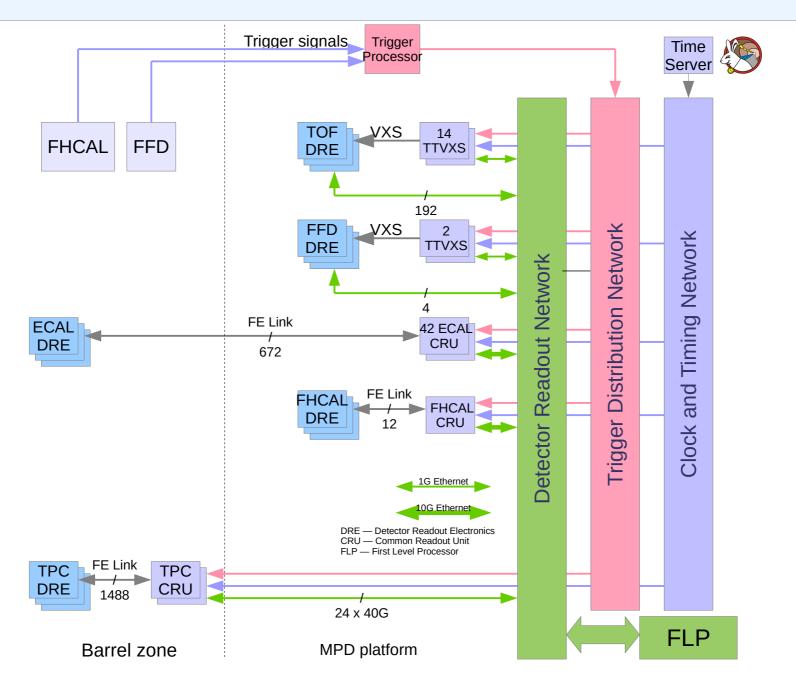

#### **TOF - VXS Readout System**

TOF DAQ is comprised of 14 VXS (VMEBus Switched Serial, ANSI/VITA-41) crates each equipped with one TTVXS and 14 TDC72VHL modules. TTVXS receives trigger information from Local Trigger Unit. Reference frequency and timestamp is provided by *Clock and Timing Network.* Module is controlled via *Front-End Control Network.* TTVXS distributes trigger and synchronous clock to TDC72VHL boards by VXS backplane. TTVXS monitors status of boards (voltages, temperature and etc).

I.Slepnev, JINR

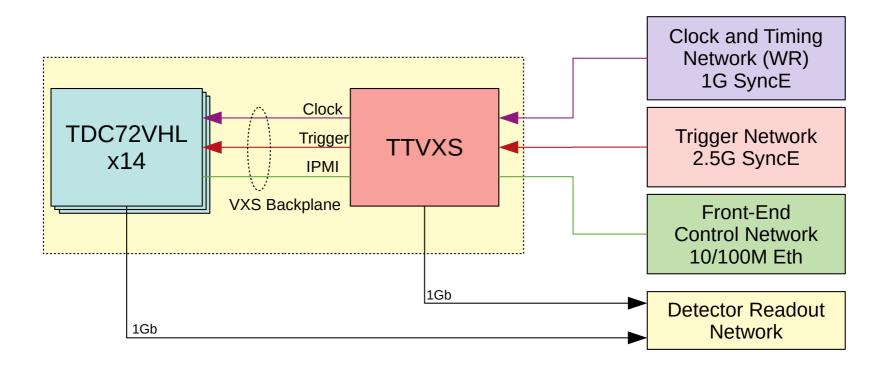

#### TTVXS — VXS Switch Board

TTVXS is a Time, Trigger and Management module for VXS crate

- Clock, timestamp and trigger distribution to VXS payload boards over VXS serial backplane

- 4 SFP+ sockets for Detector Readout, Trigger Distribution and Clock & Timing connections

- Reference frequency and timestamp provided by White Rabbit Network or FE-Link (with CRU-16)

- Additional clock and trigger interface by FMC (VITA-57) card slot integration with other systems

Status: 2 boards ready. Basic functions implemented. Testing.

#### IPMI mezzanine board

IPMI (Intelligent Platform Management) function for automatic topology discovery, module status monitoring and control, firmware update

Status: basic functions implemented, improvements ongoing

IPMI mezzanine board 3rd MPD and BM@N Collaboration meeting, 16 Apr 2019

### TDC72VHL — Multihit 25 ps Timestamping TDC

TDC72VHL board performs time-stamping of discrete signals (hits). It is based on HPTDC chip. Hit timestamps are kept for 104 us in ring type memory.

| Number of Channels         | 72                      |

|----------------------------|-------------------------|

| Input Signal               | LVDS                    |

| Input Impedance            | 100 Ohm                 |

| Input Differential Voltage | 25 mV min               |

| Input Connector            | CXP Interconnect System |

| Time Resolution with INL   | ~25 ps                  |

| Data Transfer Interface    | SFP, 1000Base-X         |

| Synchronization Interface  | TTC over VXS            |

#### **TOF & FFD DAQ Modules Production Status**

| Module   | Produced<br>and Tested | Plan<br>Q4 2019 | Plan<br>Q3 2020 | Total Qty. |

|----------|------------------------|-----------------|-----------------|------------|

| TDC72VHL | 72                     | 140             | 80              | 220        |

| TTVXS    | 2                      | 10              | 7               | 17         |

| CRU16    | -                      | 2               | -               | 2          |

TDC72VHL:

- Produced ~30%

- In 2019 to produce ~30% more

- In 2020 to produce all remainig, plus spare modules

TTVXS:

- Produced ~15%

- In 2019 to produce ~50% more

- In 2020 to produce all remainig, plus spare modules

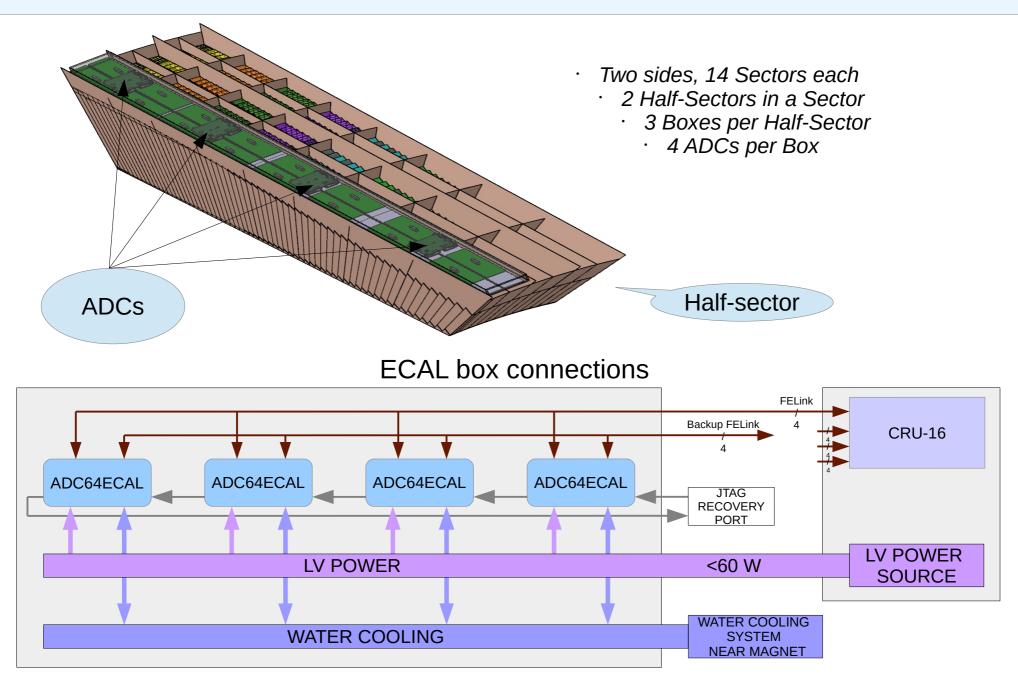

#### **ECAL Structure**

I.Slepnev, JINR

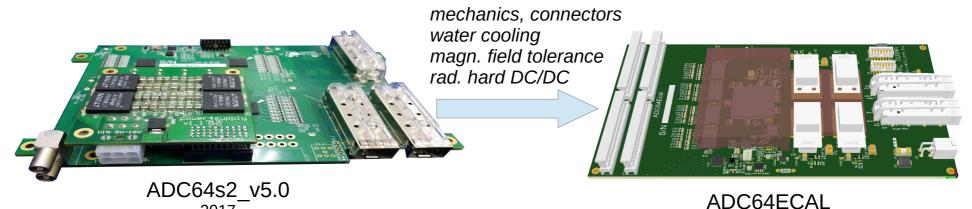

#### Waveform digitizer for ECAL – ADC64ECAL

2017 **Usage** ECal at BM@N - data taking 2018 FHCal at MPD - ready 2019

#### **Current status**

Firmware is ready Software is ready PCB in production

> **Total quantity for ECal** 672 pcs

#### ADC64ECAL board characteristics

| Number of Channels             | 64        |

|--------------------------------|-----------|

| Sample rate                    | 62.5 MS/s |

| Resolution                     | 14 bit    |

| Power consumption              | < 15 W    |

| Magnetic field tolerance       | by design |

| Radiation hard DC/DC covertors | yes       |

I.Slepnev, JINR

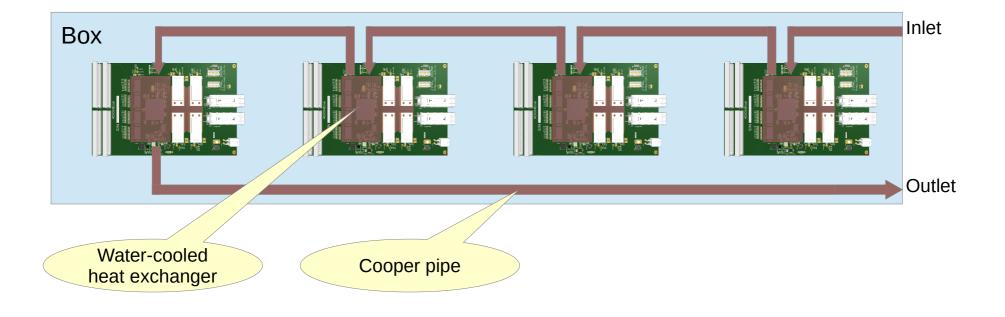

#### ECAL water cooling system concept

Status: Contract for R&D

- Leakless liquid cooling system (pressure < 0,1 MPa)

- Non magnetic matherials

- 5 years of service-less continuous operation

I.Slepnev, JINR

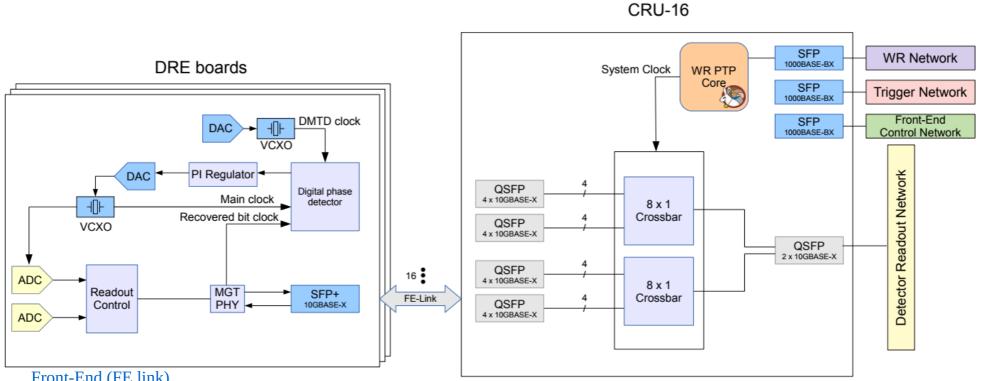

## Common Readout (and everything else) Unit

#### Front-End (FE link)

"Variable-speed Synchronous Ethernet". Byte-oriented, 8b/10b Ethernet like encoding and framing

Maximum data rate: 2.5 Gb/s VXS backplane (TTVXS), 8 Gb/s (CRU-16) with commercial QSFP fiber-optical transceivers.

DRE clock synchronized to CRU with digital PLL. Short fixed cables – one time delay calibration.

Timestamps, trigger, data readout, control over same link

No TCP-IP stack complexity in DRE. Simple FGPA code with fail-safe FSM and data pipelines to mitigate SEU events.

#### Aggregation "switch" (CRU-16 core)

Not an Ethernet switch. Fixed traffic directions: left-right or right-left only. Connects to DAQ network with 10G Ethernet, UDP-IP. Large FPGA on board running White Rabbit and service CPUs

Extensive diagnostics: hardware histograms, RAM-based multichannel counters

Use speed translation FIFOs. Arbitrated crossbars. Option for large DRAM buffer on board

Future: hardware event merging for connected DRE boards

I.Slepnev, JINR

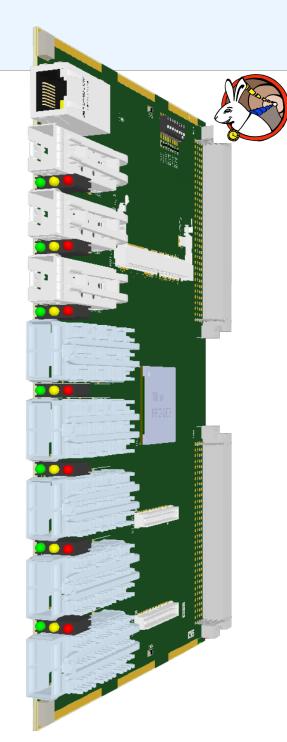

## **CRU-16**

#### Common Readout Unit for 16 DRE boards

- FE-Link interface to DRE boards multi-gigabit duplex serial synchronous interconnect with deterministic latency. Provides clock and trigger information for downstream boards and receives raw data stream

- 4 GB onboard DDR3 memory for data buffering, decouples realtime hardware data flow from software data receivers

- 4 QSFP downlink sockets for 16 Detector Readout boards connections grouped by 4

- 3 SFP sockets for Trigger Distribution, Clock & Timing

- 10/100 Ethernet for Slow Control

- Timing synchronization by White Rabbit Network

#### Status

- FE-Link designed and tested on prototype

- PCB to be ready in 2019

- Firmware and software under development

I.Slepnev, JINR

### **DAQ Control Software overview**

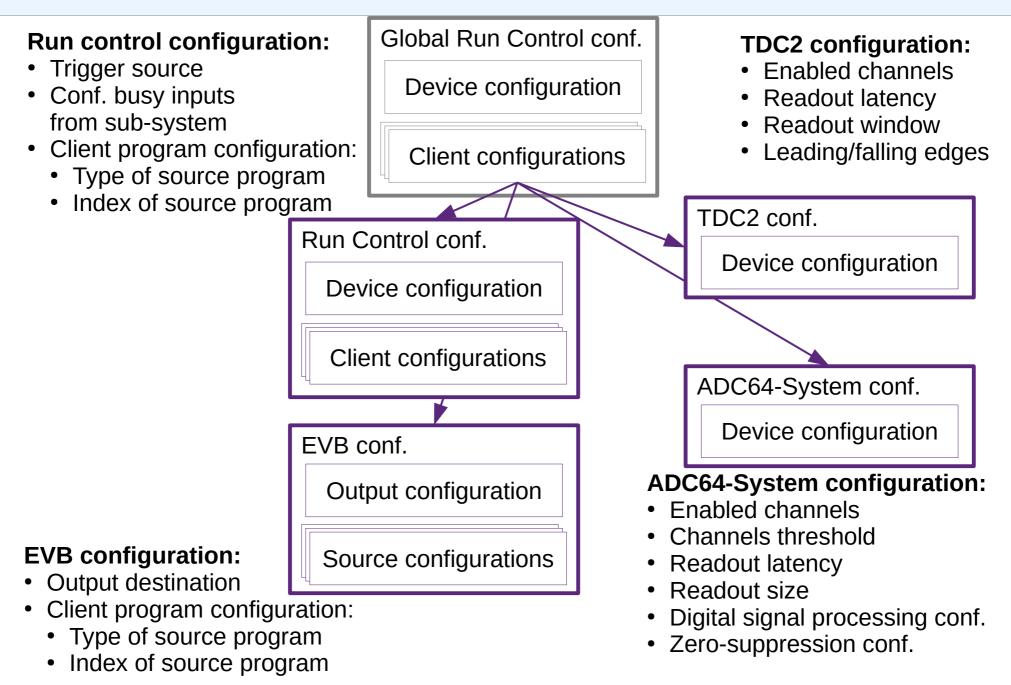

## Run configuration

I.Slepnev, JINR

## **Program configuration**

|                                          | Event builder. | Program index: tim1      |                                                                                                                                                                                                                        | _ = ×                             |           |

|------------------------------------------|----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|

| <u>F</u> ile <u>Options</u> <u>H</u> elp |                |                          |                                                                                                                                                                                                                        |                                   |           |

| Resetting                                | -              | Cor                      | nfiguration manager                                                                                                                                                                                                    |                                   | - • ×     |

| Start Stopped                            | Configurations | Last modified            | Key                                                                                                                                                                                                                    | Value                             | New       |

| Stop Starting Stopping                   | 1 default      | 12 April 2019 2:53:27 pm | advancedCounters<br>combinerOut                                                                                                                                                                                        | false<br>file                     | Rename    |

| Started Error                            | 2 343          | 20 March 2019 1:54:39 pm | combinerOutTcpNum                                                                                                                                                                                                      | 1                                 | Clone     |

| mp                                       | з d            | 06 March 2019 10:1:56 am | configuration_name<br>date_of_creation                                                                                                                                                                                 | d46<br>4/12/19 2:53 PM            | Delete    |

|                                          | 4 d1.2         | 04 March 2019 2:24:6 pm  | evNumberStep<br>geometry                                                                                                                                                                                               | 1<br>false                        | Switch to |

|                                          | 5 d45.2        | 06 March 2019 10:5:34 am | isRemoteEnabled<br>monitorPort                                                                                                                                                                                         | true<br>0                         | Switch to |

| id readout Online type ir                | 6 f3           | 04 March 2019 2:26:1 pm  | outputBufSize                                                                                                                                                                                                          | 20480000                          |           |

| 1 1 ✓ X MStream 0x0a                     | 7 f4           | 06 March 2019 10:5:31 am | program_index<br>program_type                                                                                                                                                                                          | tim1<br>EvB                       |           |

| 2 2 <b>√ √</b> EvB DCH                   | <b>8</b> d46   | 12 April 2019 2:53:44 pm | startEvNumber<br>storageDir                                                                                                                                                                                            | 0<br>/ceph/afi/afi-daq-3/TDC72VXS |           |

|                                          |                |                          | <pre>storageDir /cepin/air/air/dad-3/10C/20/ timeDistrEn false window_state false * client-1 index 0x0a7a7898 inputBufSize 0 readout true type MStream * client-2 index DCH inputBufSize 0 readout true type EvB</pre> |                                   | Close     |

|                                          |                |                          |                                                                                                                                                                                                                        |                                   |           |

- Stores all parameters which relate only to this program.

- Allow to fast switch from calibration to data taking work.

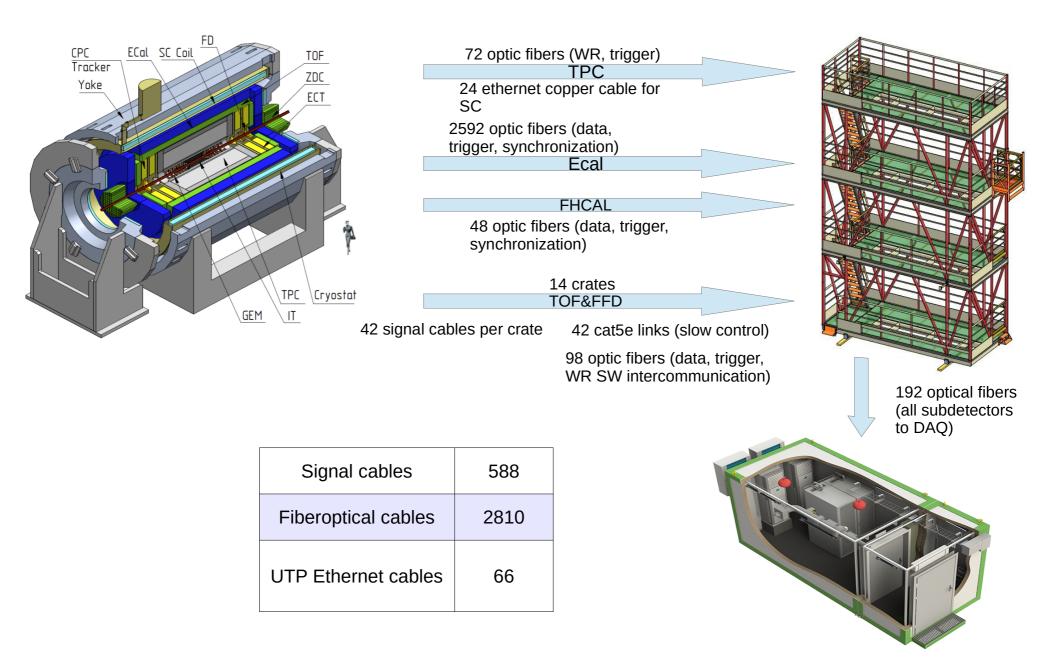

## MPD DAQ Cable Connections (Stage-1)

I.Slepnev, JINR

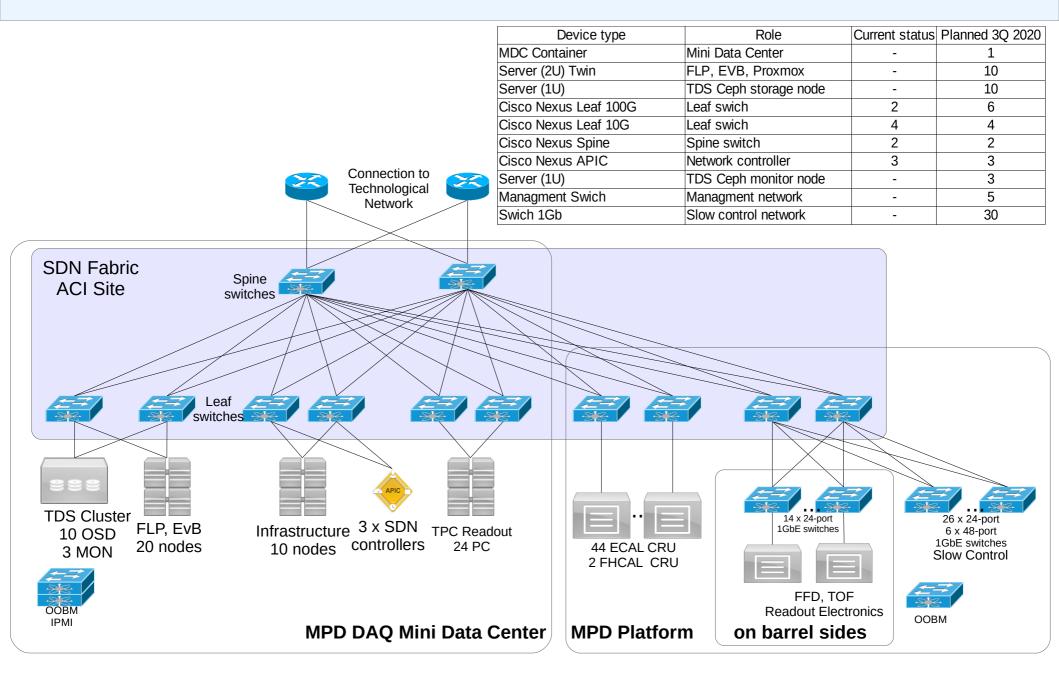

### MPD DAQ Network

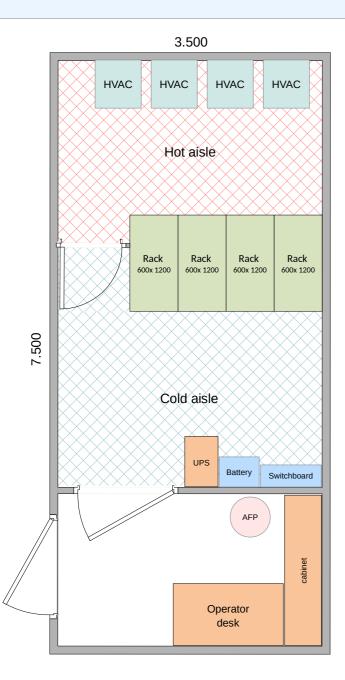

### MPD DAQ – Mini Data Center

| Specifications |                         |  |

|----------------|-------------------------|--|

| Input power    | 50 kW                   |  |

| IT power       | 24 kW (N+1) / 30 kW max |  |

| Rack count     | 4 racks                 |  |

| Redundancy     | N+1 (UPS, HVAC)         |  |

| Battery backup | 8 minutes               |  |

| Rack size      | 600 x 1200 x 42U        |  |

| Stage-1 Equipment                         | Rack Units |

|-------------------------------------------|------------|

| Passive network                           | 16         |

| Active network<br>(switches, controllers) | 18         |

| Infrastructure nodes                      | 4          |

| FLP, Event Builder nodes                  | 44         |

| Transient Flash Storage                   | 13         |

| Message Logging and Search                | 5          |

| Reserve (Stage-2)                         | 68         |

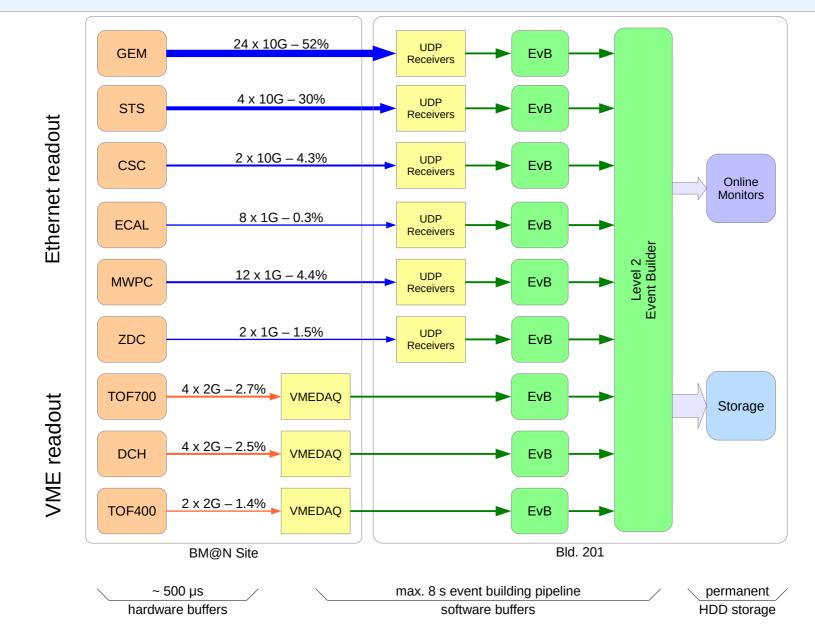

# BM@N DAQ setup in March 2018

#### BM@N Mini Data Center, bld. 205

## Thank you!

I.Slepnev, JINR

I.Slepnev, JINR

#### Extra slides

I.Slepnev, JINR

#### **MPD Data Flow**